# OpenSPARC<sup>™</sup> T2 Processor Megacell Specification

Sun Microsystems, Inc. www.sun.com

Part No. 820-2728-10 December 2007, Revision A

Submit comments about this document at: http://www.sun.com/hwdocs/feedback

Copyright © 2007 Sun Microsystems, Inc., 4150 Network Circle, Santa Clara, California 95054, U.S.A. All rights reserved.

Sun Microsystems, Inc. has intellectual property rights relating to technology embodied in the product that is described in this document. In particular, and without limitation, these intellectual property rights may include one or more of the U.S. patents listed at http://www.sun.com/patents and one or more additional patents or pending patent applications in the U.S. and in other countries.

U.S. Government Rights - Commercial software. Government users are subject to the Sun Microsystems, Inc. standard license agreement and applicable provisions of the FAR and its supplements.

Use is subject to license terms.

This distribution may include materials developed by third parties.

Sun, Sun Microsystems, the Sun logo, Solaris, OpenSPARC T1, OpenSPARC T2 and UltraSPARC are trademarks or registered trademarks of Sun Microsystems, Inc. in the U.S. and other countries.

All SPARC trademarks are used under license and are trademarks or registered trademarks of SPARC International, Inc. in the U.S. and other countries. Products bearing SPARC trademarks are based upon architecture developed by Sun Microsystems, Inc.

UNIX is a registered trademark in the U.S. and other countries, exclusively licensed through X/Open Company, Ltd.

The Adobe logo is a registered trademark of Adobe Systems, Incorporated.

Products covered by and information contained in this service manual are controlled by U.S. Export Control laws and may be subject to the export or import laws in other countries. Nuclear, missile, chemical biological weapons or nuclear maritime end uses or end users, whether direct or indirect, are strictly prohibited. Export or reexport to countries subject to U.S. embargo or to entities identified on U.S. export exclusion lists, including, but not limited to, the denied persons and specially designated nationals lists is strictly prohibited.

Sun makes no representation that the OpenSPARC T2 design model or its implementation does not infringe any third party patents or other intellectual property rights.

DOCUMENTATION AND REGISTER TRANSFER LEVEL (RTL) ARE PROVIDED "AS IS", AND ALL EXPRESS OR IMPLIED CONDITIONS, REPRESENTATIONS AND WARRANTIES, INCLUDING ANY IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT, ARE DISCLAIMED, EXCEPT TO THE EXTENT THAT SUCH DISCLAIMERS ARE HELD TO BE LEGALLY INVALID.

Copyright © 2007 Sun Microsystems, Inc., 4150 Network Circle, Santa Clara, California 95054, Etats-Unis. Tous droits réservés.

Sun Microsystems, Inc. détient les droits de propriété intellectuels relatifs à la technologie incorporée dans le produit qui est décrit dans ce document. En particulier, et ce sans limitation, ces droits de propriété intellectuelle peuvent inclure un ou plus des brevets américains listés à l'adresse http://www.sun.com/patents et un ou les brevets supplémentaires ou les applications de brevet en attente aux Etats - Unis et dans les autres pays.

L'utilisation est soumise aux termes de la Licence.

Cette distribution peut comprendre des composants développés par des tierces parties.

Sun, Sun Microsystems, le logo Sun, Solaris, OpenSPARC T1, OpenSPARC T2 et UltraSPARC sont des marques de fabrique ou des marques déposées de Sun Microsystems, Inc. aux Etats-Unis et dans d'autres pays.

Toutes les marques SPARC sont utilisées sous licence et sont des marques de fabrique ou des marques déposées de SPARC International, Inc. aux Etats-Unis et dans d'autres pays. Les produits portant les marques SPARC sont basés sur une architecture développée par Sun Microsystems, Inc.

UNIX est une marque déposée aux Etats-Unis et dans d'autres pays et licenciée exlusivement par X/Open Company, Ltd.

Le logo Adobe. est une marque déposée de Adobe Systems, Incorporated.

Les produits qui font l'objet de ce manuel d'entretien et les informations qu'il contient sont regis par la legislation americaine en matiere de controle des exportations et peuvent etre soumis au droit d'autres pays dans le domaine des exportations et importations. Les utilisations finales, ou utilisateurs finaux, pour des armes nucleaires, des missiles, des armes biologiques et chimiques ou du nucleaire maritime, directement ou indirectement, sont strictement interdites. Les exportations ou reexportations vers des pays sous embargo des Etats-Unis, ou vers des entites figurant sur les listes d'exclusion d'exportation americaines, y compris, mais de maniere non exclusive, la liste de personnes qui font objet d'un ordre de ne pas participer, d'une facon directe ou indirecte, aux exportations des produits ou des services qui sont regi par la legislation americaine en matiere de controle des exportations et la liste de ressortissants specifiquement designes, sont rigoureusement interdites.

LA DOCUMENTATION EST FOURNIE "EN L'ETAT" ET TOUTES AUTRES CONDITIONS, DECLARATIONS ET GARANTIES EXPRESSES OU TACITES SONT FORMELLEMENT EXCLUES, DANS LA MESURE AUTORISEE PAR LA LOI APPLICABLE, Y COMPRIS NOTAMMENT TOUTE GARANTIE IMPLICITE RELATIVE A LA QUALITE MARCHANDE, A L'APTITUDE A UNE UTILISATION PARTICULIERE OU A L'ABSENCE DE CONTREFACON.

## Contents

### Preface xix

| 1. Megacells in th | e OpenSPARC T2 Processor | 1–1 |

|--------------------|--------------------------|-----|

|--------------------|--------------------------|-----|

1.1 Overview 1–1

### 2. Store Buffer CAM (SCM) 2–1

- 2.1 Functional Description 2–1

- 2.1.1 General 2–1

- 2.1.2 Lookup Operation 2–2

- 2.1.3 Read Operation 2–2

- 2.1.4 Write Operation 2–2

- 2.2 Block Diagram 2–3

- 2.3 Pipeline Diagram 2–5

- 2.4 I/O List 2-6

- 2.4.1 Modes of Operation 2–7

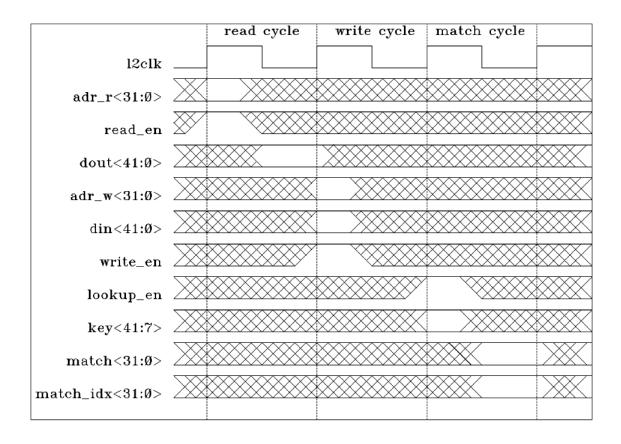

- 2.5 Timing Diagram 2–8

### 3. Translation Lookaside Buffer (TLB) 3-1

- 3.1 Functional Description 3–1

- 3.1.1 OpenSPARC T1 vs OpenSPARC T2 3-1

- 3.1.2 DTLB Description 3–2

- 3.1.3 ITLB Description 3–2

- 3.2 Block Diagrams 3–4

- 3.3 I/O List 3-6

- 3.3.1 IDTLB/ITLB Modes of Operation 3-8

- 3.3.1.1 Primary Operations 3–8

- 3.3.1.2 Secondary Operations 3–8

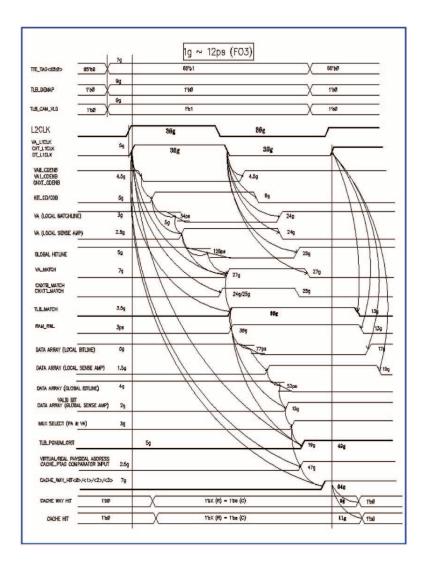

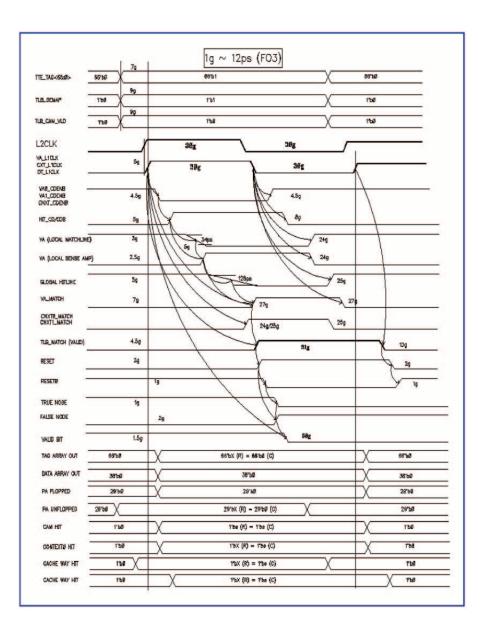

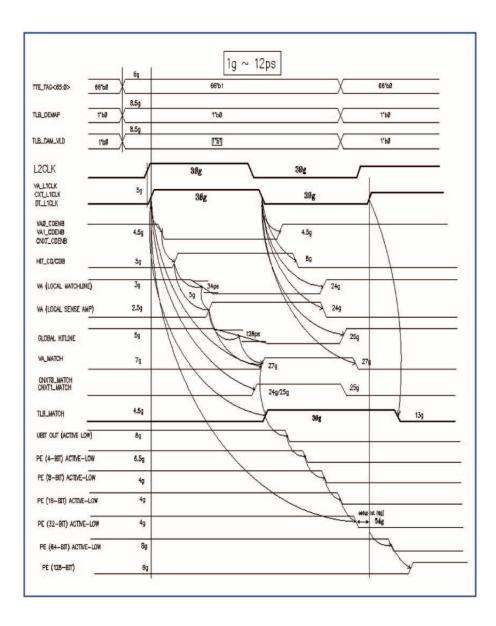

- 3.4 Timing Diagrams 3–11

### 4. Integer Register File (IRF) 4–1

- 4.1 Functional Description 4–1

- 4.1.1 General 4–2

- 4.1.2 Read/Write Operations 4–3

- 4.1.3 Save/Restore Operations 4–3

- 4.1.4 Illegal Operations 4–3

- 4.2 Block Diagram 4–4

- 4.3 I/O List 4–5

- 4.4 Functional Operation 4–8

- 4.5 Timing Diagram 4–8

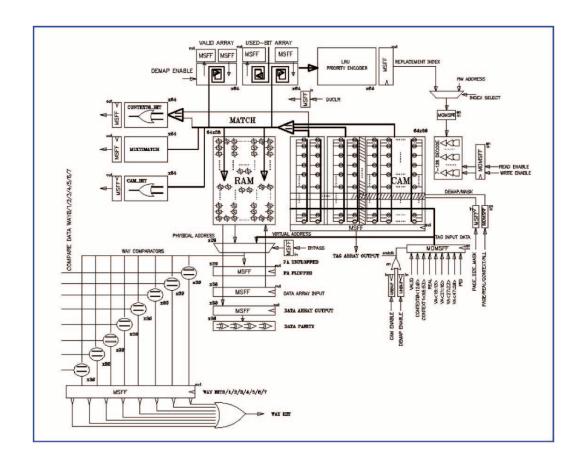

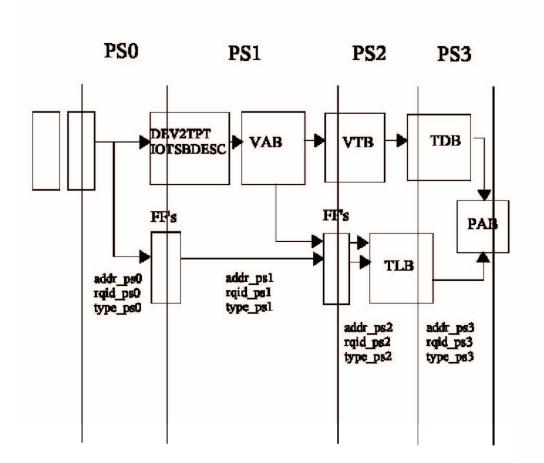

### 5. Memory Management Unit CAM 5–1

- 5.1 Functional Description 5–1

- 5.2 Block Diagram 5–4

- 5.3 I/O List 5-6

- 5.4 Functional Operation 5–7

- 5.5 Timing Diagrams 5–8

### 6. Floating-point Register File (FRF) 6–1

- 6.1 Functional Description 6–1

- 6.2 Block Diagrams 6–4

- 6.3 I/O List 6–5

- 6.4 Functional Operation 6–6

- 6.5 Timing Diagram 6–7

### 7. Instruction Cache Data Array (ICD) 7–1

- 7.1 Functional Description 7–1

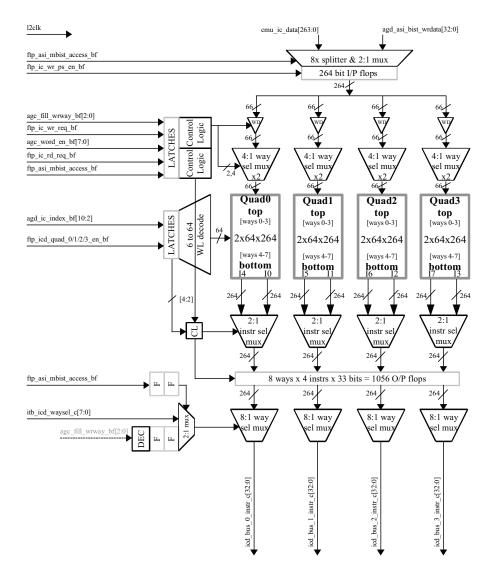

- 7.2 Block Diagram 7–3

- 7.3 I/O List 7–4

- 7.4 Functional Table 7–6

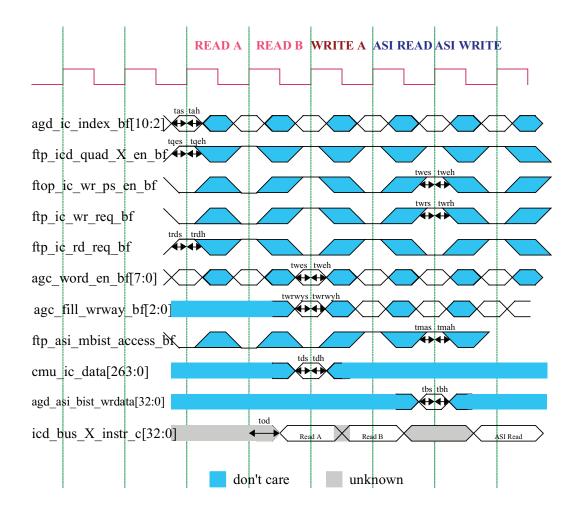

- 7.5 Timing Diagram 7–9

### 8. Instruction Cache Tag Array (ICT) 8–1

- 8.1 Functional Description 8–1

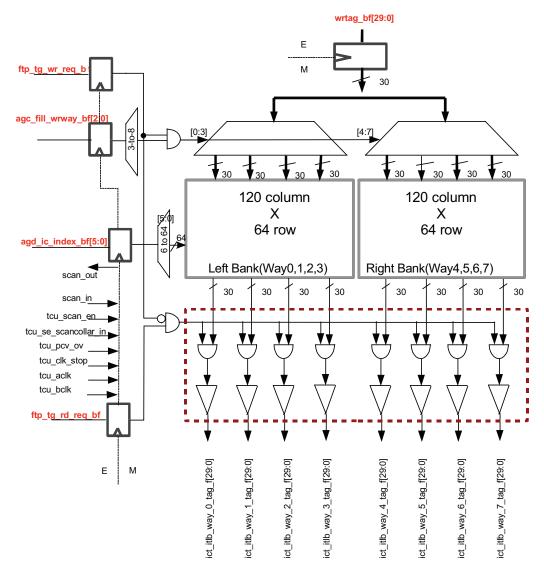

- 8.2 Block Diagrams 8–3

- 8.3 I/O List 8-4

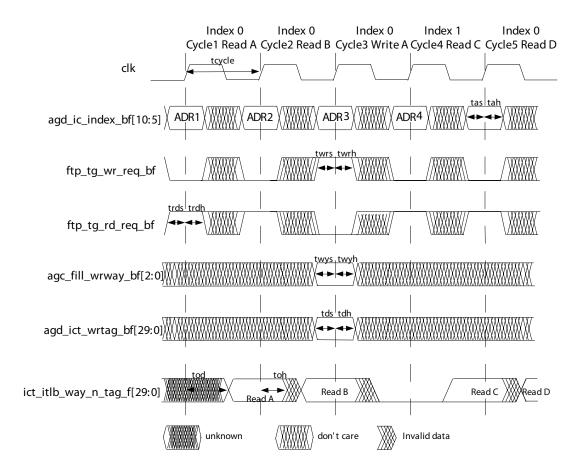

- 8.4 Timing Diagrams 8–5

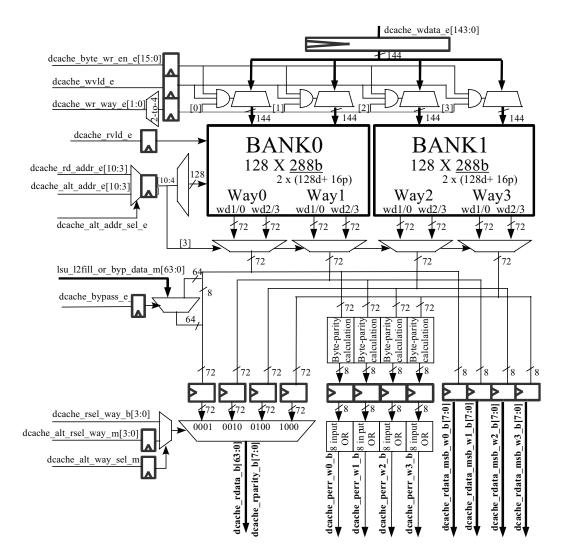

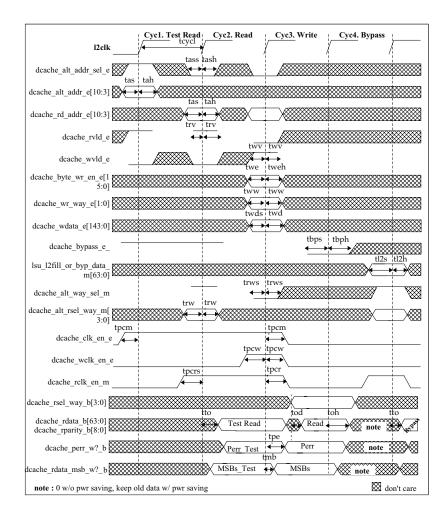

### 9. Data Cache Array (DCA) 9–1

- 9.1 Functional Description 9–1

- 9.2 Block Diagram 9–2

- 9.3 I/O List 9-4

- 9.4 Functional Table 9–6

- 9.5 Timing Diagram 9–7

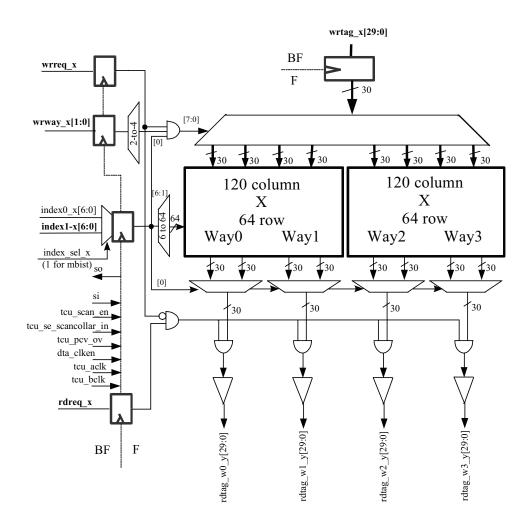

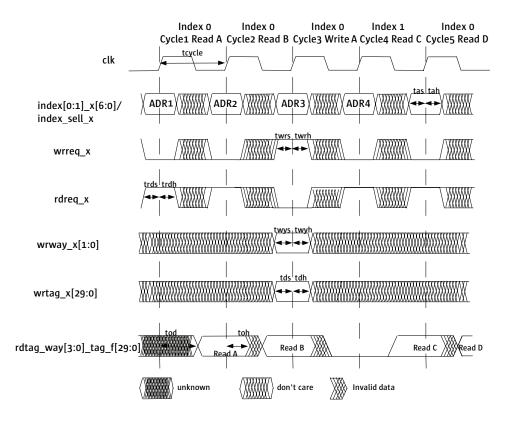

### 10. Data Cache Tag Array (DTA) 10–1

- 10.1 Functional Description 10–1

- 10.2 Block Diagrams 10–3

- 10.3 I/O List 10–4

- 10.4 Functional Table 10–5

- 10.5 Timing Diagram 10–6

### 11. Data Valid Bit Array (DVA) 11-1

- 11.1 Functional Description 11–1

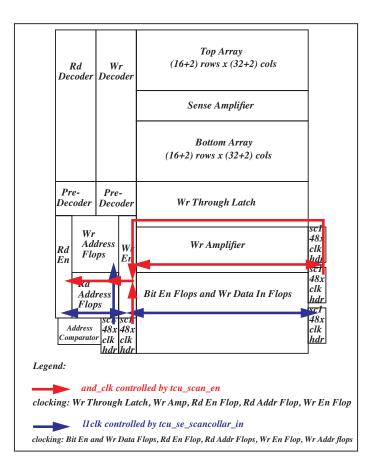

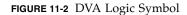

- 11.2 Block Diagrams 11–2

- 11.3 I/O List 11–3

- 11.4 Functional Table 11–5

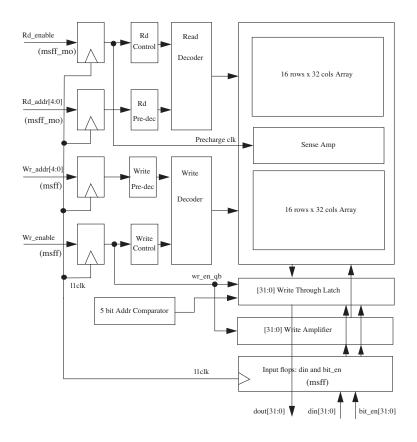

- 11.5 Timing Diagram 11–5

### 12. L2-Cache Tag Array 12–1

- 12.1 Functional Description 12–1

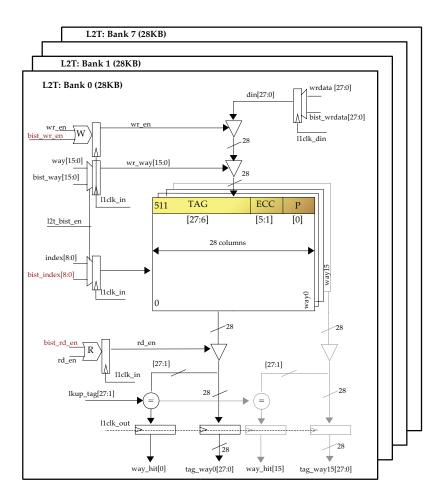

- 12.2 Block Diagram 12–3

- 12.3 I/O List 12-4

- 12.4 Functional Operation 12–7

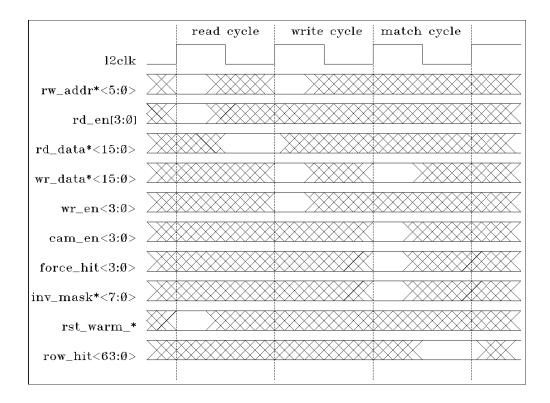

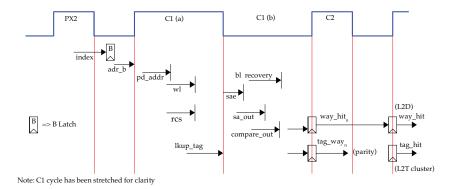

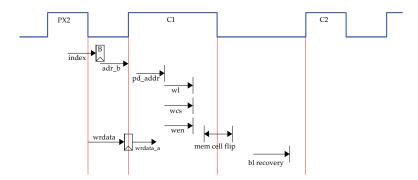

- 12.5 Timing Diagrams 12-8

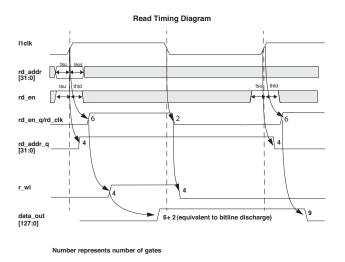

- 12.5.1 Read Timing Diagram 12–9

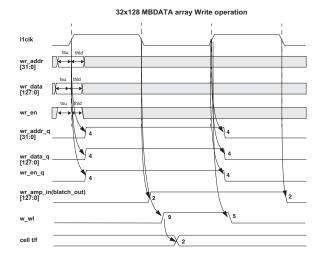

- 12.5.2 Write Timing Diagram 12–9

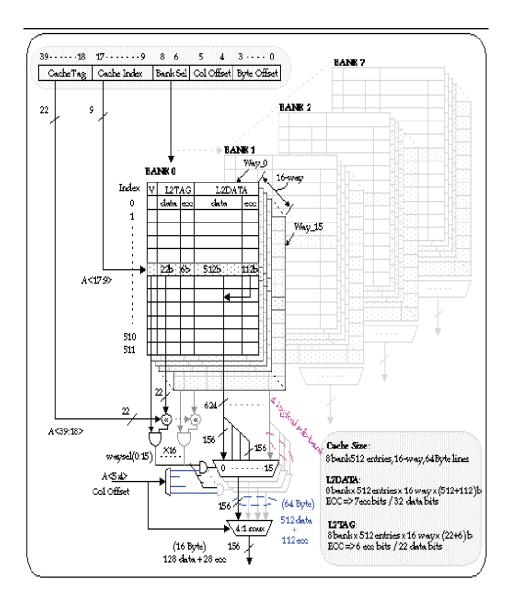

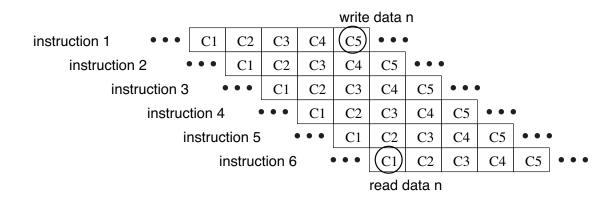

### 13. L2-Cache Data Array 13–1

- 13.1 Functional Description 13–1

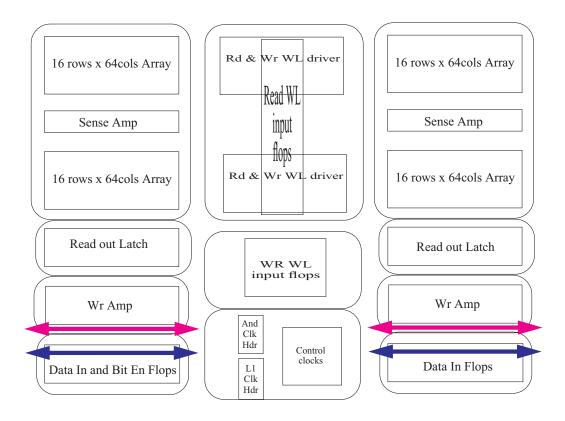

- 13.2 Block Diagrams 13–3

- 13.3 I/O List 13–5

- 13.4 Timing Diagrams 13–7

#### 14. L2-Cache Miss Buffer Data Array 14–1

- 14.1 Functional Description 14–1

- 14.2 Block Diagrams 14–2

- 14.3 I/O List 14–3

- 14.4 Functional Operations 14–4

- 14.4.1 Pipeline Diagrams 14–5

- 14.5 Timing Diagrams 14–6

### 15. L2-Cache Miss Buffer Request CAM 15–1

- 15.1 Functional Description 15–1

- 15.2 Block Diagram 15–3

- 15.3 Pipeline Diagram 15–4

- 15.4 I/O List 15-4

- 15.5 Functional Operations 15–5

- 15.6 Timing Diagram 15–7

### 16. L2-Cache Instruction and Data Directory CAM 16–1

- 16.1 Functional Description 16–1

- 16.1.1 Instruction Cache Directory 16–1

- 16.1.2 Data Cache Directory 16–2

- 16.2 Block Diagrams 16–5

- 16.3 Pipeline Diagram 16–6

- 16.4 I/O List 16–7

- 16.5 Functional Operations 16-8

- 16.6 Timing Diagram 16–9

#### 17. L2-Cache Fill Buffer 17–1

17.1 Functional Description 17–1

17.1.1 Writeback Buffer 17–2

- 17.2 Block Diagram 17–3

- 17.3 I/O List 17–3

- 17.3.1 Pipeline Diagram 17–5

- 17.4 Functional Operations 17–5

- 17.5 Timing Diagram 17–6

### 18. L2-Cache Dual Port Register File (16x160) 18–1

- 18.1 Functional Description 18–1

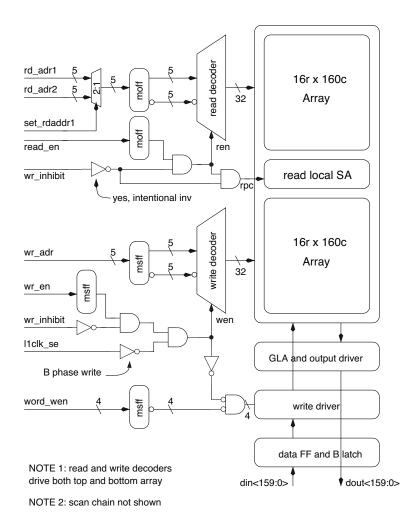

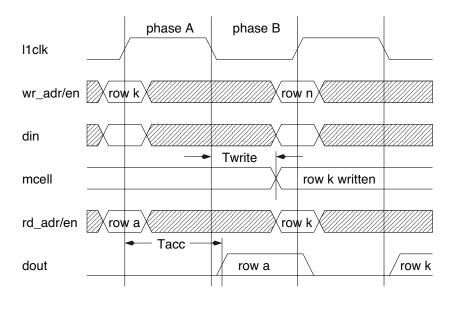

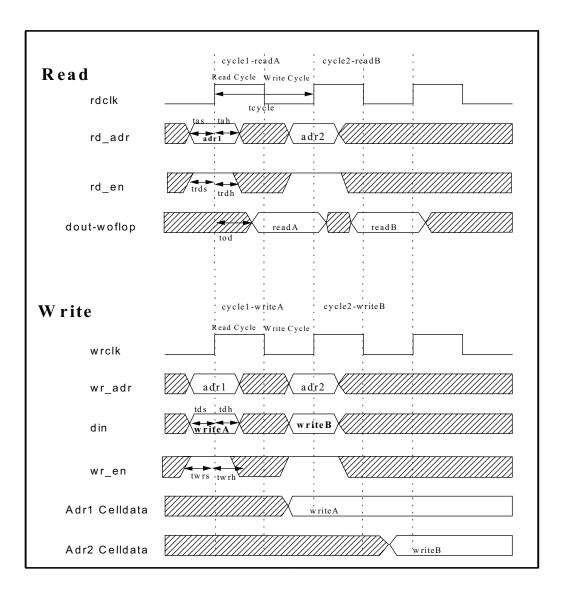

- 18.2 Block Diagrams 18–3

- 18.3 I/O List 18–4

- 18.4 Functional Operation 18–5

- 18.5 Timing Diagrams 18–6

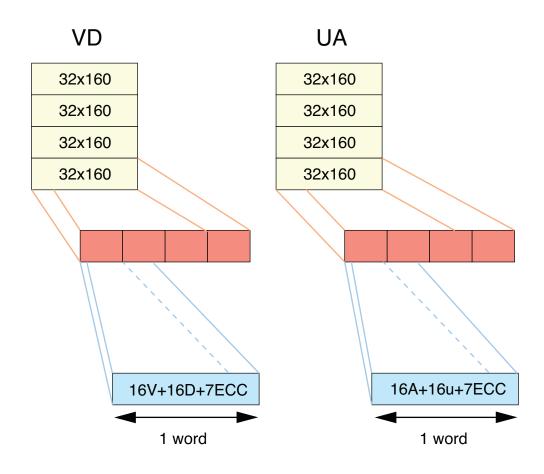

### 19. L2-Cache VUAD Register File (32x160) 19–1

- 19.1 Functional Description 19–1

- 19.2 Block Diagram 19–3

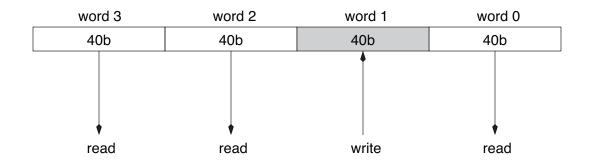

- 19.3 Functional Operation 19–419.3.1 Partial Entry Read and Write 19–4

- 19.4 Pipeline Diagram 19–5

- 19.5 Logic Diagram 19–6

- 19.6 I/O Signal List 19–7

- 19.7 Timing Diagram 19–8

### 20. Memory Controller Register File (MCU 32x72) 20–1

- 20.1 Functional Description 20–1

- 20.1.1 Read Operations 20–2

- 20.1.2 Write Operations 20–2

- 20.2 I/O List 20-3

- 20.3 Functional Table 20-4

- 20.4 Timing Diagram 20-4

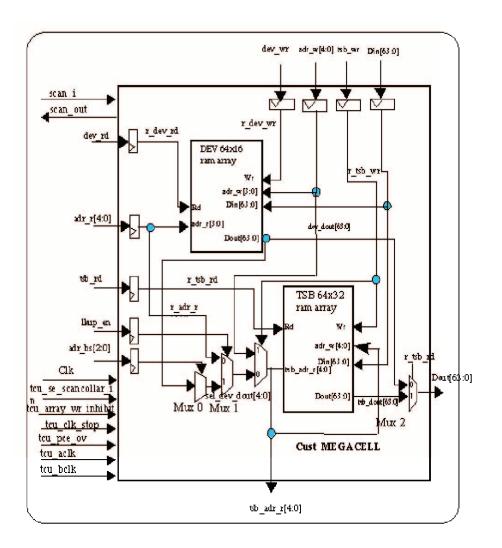

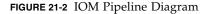

#### 21. Data Management Unit IOMMU Array 21–1

- 21.1 Functional Description 21–1

- 21.2 Block Diagram 21–2

- 21.3 I/O List 21-4

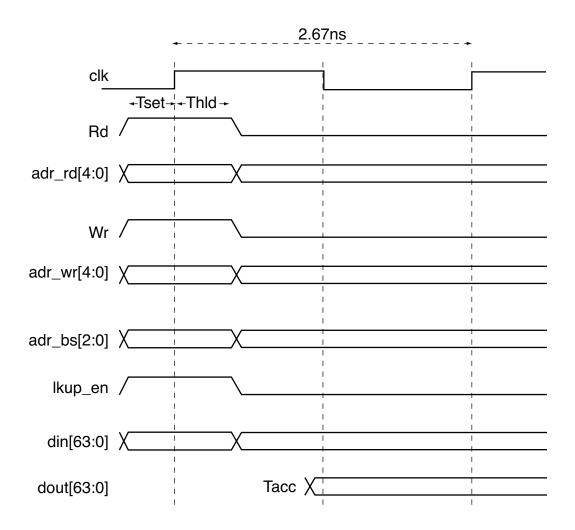

- 21.4 Functional Operation 21–5

- 21.5 Timing Diagrams 21–6

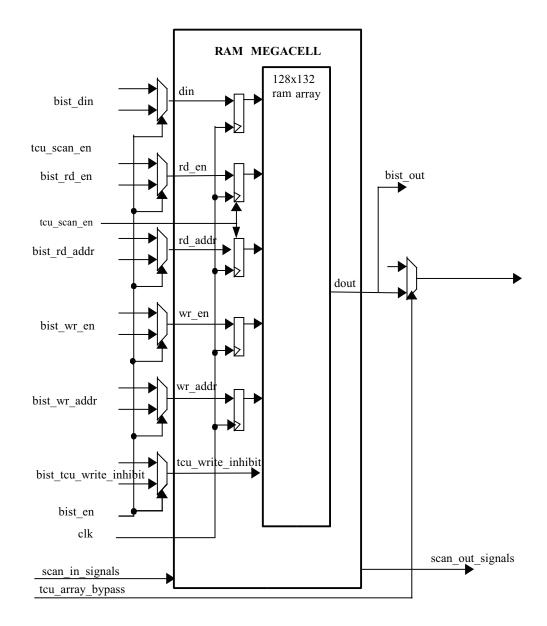

### 22. Data Management Unit (128x132) Register File 22–1

22.1 Functional Description 22–1

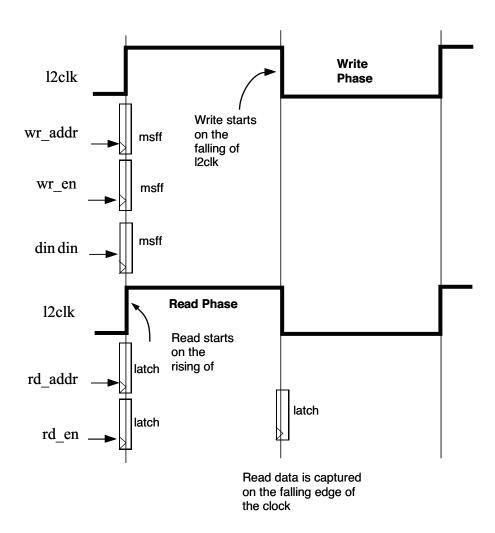

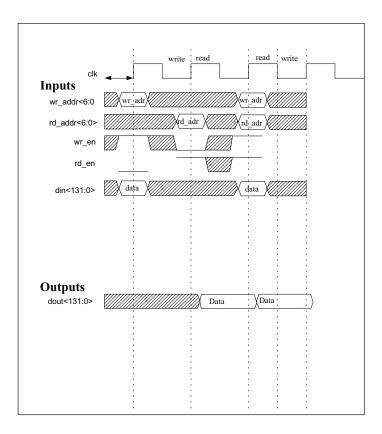

- 22.1.1 Read Operation 22-2

- 22.1.2 Write Operation 22–2

- 22.2 Block Diagrams 22–3

- 22.3 I/O List 22-5

- 22.4 Functional Operation 22–6

- 22.5 Timing Diagrams 22–7

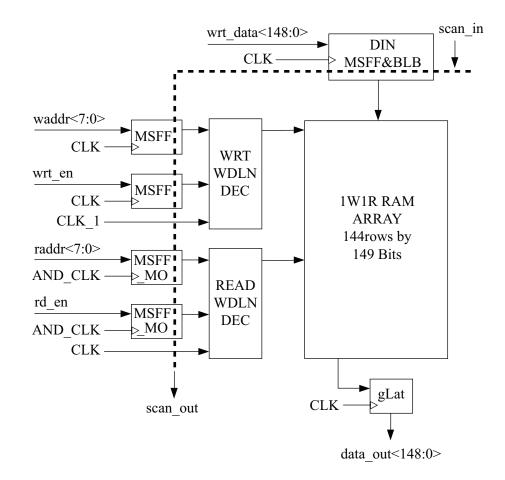

### 23. Data Management Unit (144x149) Array 23–1

- 23.1 Functional Description 23–1

- 23.1.1 Read Operation 23–2

- 23.1.2 Write Operation 23–2

- 23.2 Block Diagram 23–3

- 23.3 I/O List 23-4

- 2.5 Functional Operation 23–5

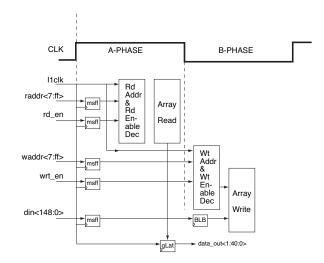

- 23.4 Timing Diagrams 23-6

### 24. Data Management Unit (512x60)Register File 24–1

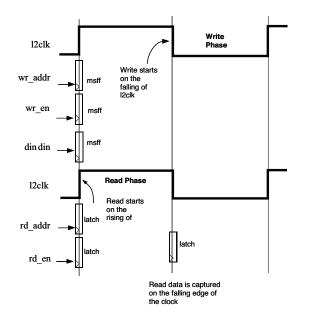

- 24.1 Functional Description 24–1

- 24.1.1 Read Operation 24–2

- 24.1.2 Write Operation 24–2

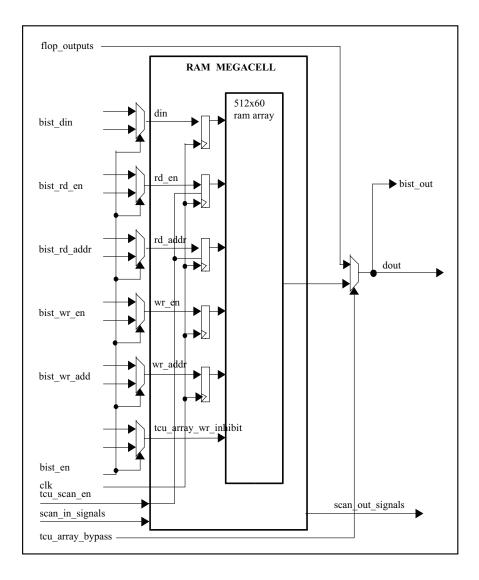

- 24.2 Block Diagrams 24–3

- 24.3 I/O List 24-4

- 24.4 Functional Operation 24–5

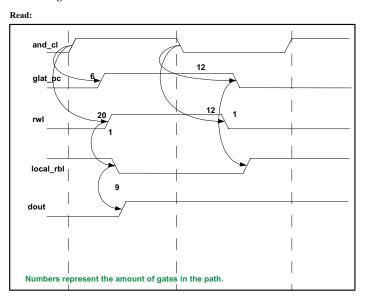

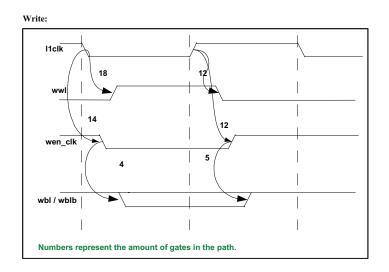

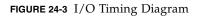

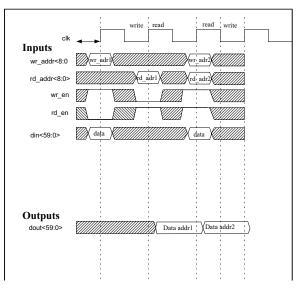

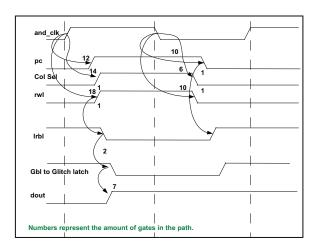

- 24.5 Timing Diagrams 24–6

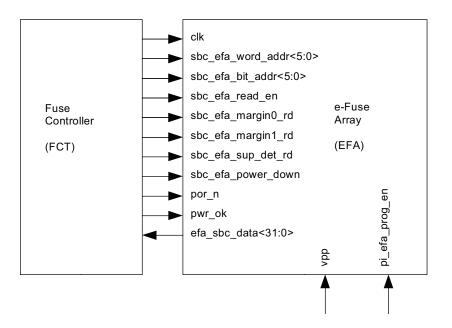

### 25. e-Fuse Array 25–1

- 25.1 Functional Description 25–1

- 25.2 EFA Interfaces 25–1

- 25.3 I/O List 25-3

Glossary Glossary-1

# Figures

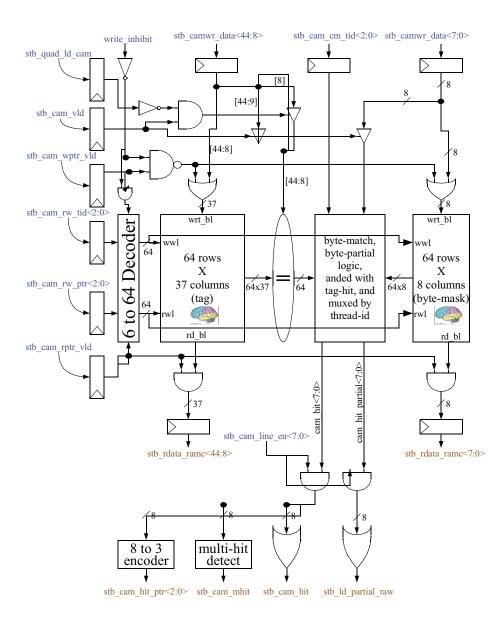

- FIGURE 2-1 SCM Block Diagram 2–3

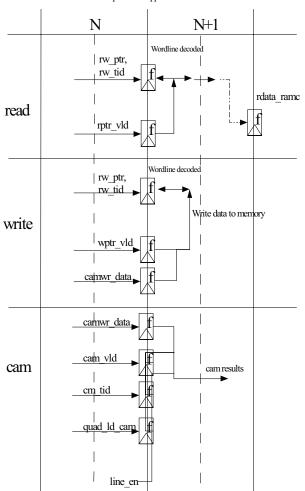

- FIGURE 2-2 SCM Pipeline Diagram 2–5

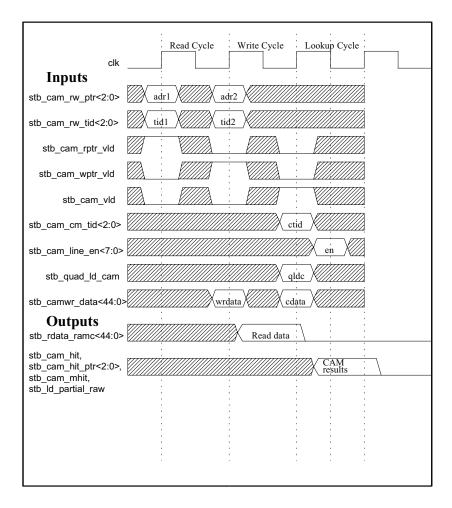

- FIGURE 2-3 SCM Timing Diagram 2–8

- FIGURE 3-1 DTLB Block Diagram 3–4

- FIGURE 3-2 ITLB Block Diagram 3–5

- FIGURE 3-3 I/O Timing Diagrams (CAM 3–11

- FIGURE 3-4 I/O Timing Diagrams (Demap) 3–12

- FIGURE 3-5 I/O Timing Diagrams (Replacement Index) 3–13

- FIGURE 3-6 I/O Timing Diagrams (Mutlimatch/Context0 Hit/Cam Hit) 3–14

- FIGURE 3-7 I/O Timing Diagrams (Write) 3–15

- FIGURE 4-1 Register File Window Structure 4–2

- FIGURE 4-2 IRF Block Diagram 4–4

- FIGURE 4-3 IRF Read Timing Diagram 4–9

- FIGURE 4-4 IRF Write Timing Diagram 4–9

- FIGURE 5-1 MMU Block Diagram 5–4

- FIGURE 5-2 Pipeline Diagram 5–5

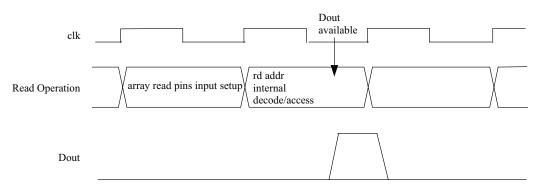

- FIGURE 5-3 I/O Timing Diagram 5–8

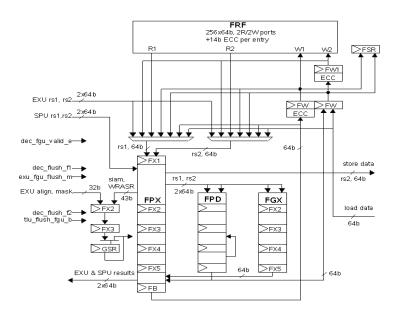

- FIGURE 6-1 FRF Block Diagram 6–4

- FIGURE 6-2 Pipeline Diagram 6–4

- FIGURE 6-3 I/O Timing Diagram 6–7

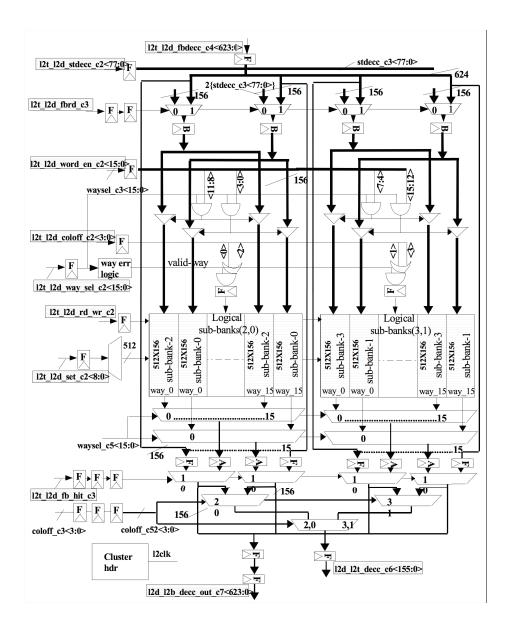

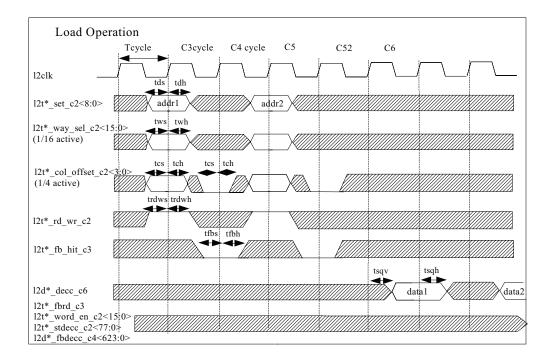

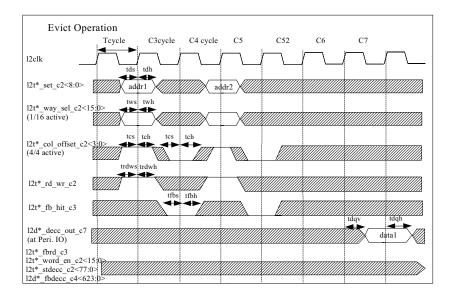

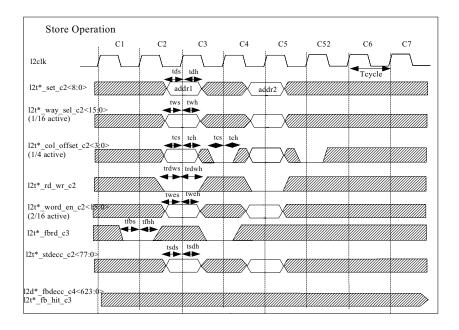

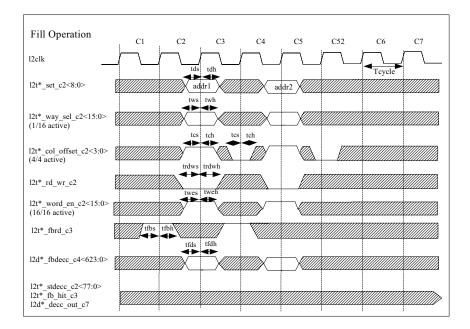

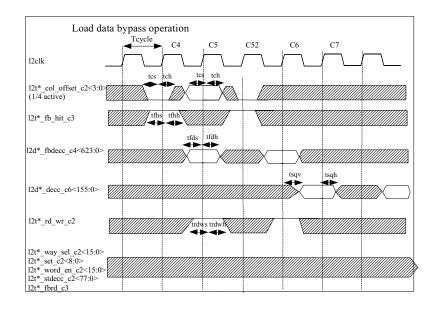

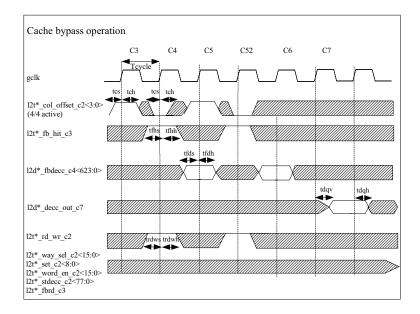

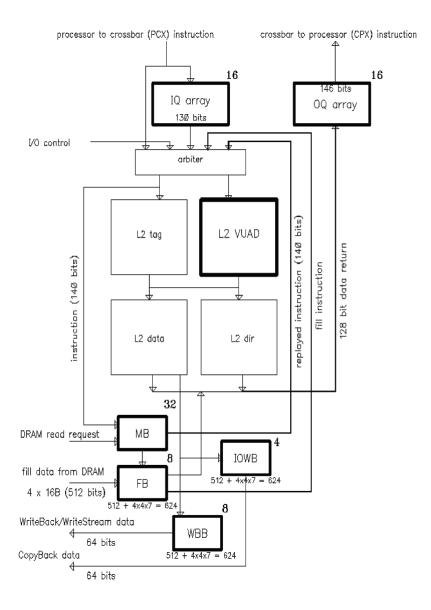

FIGURE 7-1 ICD Block Diagram 7–3 FIGURE 7-2 Read/Write Timing Diagram for ICD Array 7–9 FIGURE 8-1 ICT Block Diagram 8–3 FIGURE 8-2 Read/Write Timing Diagram of ICT Array 8–5 FIGURE 9-1 DCA Block Diagram 9–3 FIGURE 9-2 I/O Timing 9–7 FIGURE 10-1 DTA Block Diagram 10–3 FIGURE 10-2 Read/Write Timing Diagram of DTA 10–6 FIGURE 11-1 DVA Block Diagram 11–2 FIGURE 11-2 DVA Logic Symbol 11-4 FIGURE 11-3 DVA I/ORead Timing 11-6 FIGURE 11-4 DVA I/O Write Timing 11-6 FIGURE 12-1 L2 Tag Array Block Diagram 12–3 FIGURE 12-2 I/O Read Timing Diagram of L2 Tag 12–9 FIGURE 12-3 I/O Write Timing Diagram of L2 Tag 12–9 FIGURE 13-1 L2 Cache Data Array Block Diagram 13–3 Functional Block Diagram of 1 Bank of L2 Data Array 13–4 FIGURE 13-2 FIGURE 13-3 L2data Load Operation 13-7 FIGURE 13-4 L2data Evict Operation 13-8 FIGURE 13-5 L2data Store Operation 13–8 L2data Fill Operation 13-9 FIGURE 13-6 FIGURE 13-7 L2data Load Data Bypass Operation 13-9 FIGURE 13-8 L2data Cache Bypass Operation 13–10 FIGURE 14-1 Miss Buffer Data Array Block Diagram 14–2 FIGURE 14-2 Miss Buffer Data Array Logical Diagram (right half of block) 14–5 Miss Buffer Data Array Read Timing Diagram 14–6 FIGURE 14-3 FIGURE 14-4 Miss Buffer Data Array Write Timing Diagram 14–6 FIGURE 15-1 Miss Bufferrequest CAM Block Diagram 15–3 FIGURE 15-2 Miss Buffer Request CAM Timing Diagram 15–7 FIGURE 16-1 Instruction Cache and Data Cache Block Diagram 16–5

- FIGURE 16-2 I/O Timing Diagram 16–9

- FIGURE 17-1 Fill Buffer Block Diagram 17–3

- FIGURE 17-2 Fill Buffer I/O Timing Diagram 17–6

- FIGURE 18-1 Dual Port Register File (16x160) Block Diagram 18–3

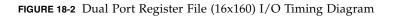

- FIGURE 18-2 Dual Port Register File (16x160) I/O Timing Diagram 18–6

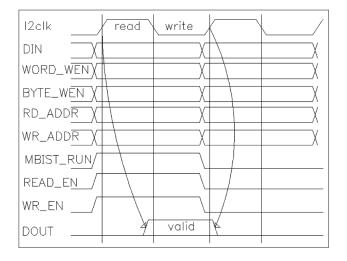

- FIGURE 18-3 Dual Port Register File (16x160) Internal Timing, Read 18–7

- FIGURE 18-4 Dual Port Register File (16x160) Internal Timing, Write 18–7

- FIGURE 19-1 VUAD (32x160) Register File Block Diagram 19–3

- FIGURE 19-2 Partial Entry Read and Write 19–5

- FIGURE 19-3 Pipeline Diagram 19–5

- FIGURE 19-4 Logic/Functional Diagram 19–6

- FIGURE 19-5 VUAD I/O Timing Diagram 19–8

- FIGURE 20-1 MCU I/O Timing 20–5

- FIGURE 21-1 IOM Block Diagram 21–2

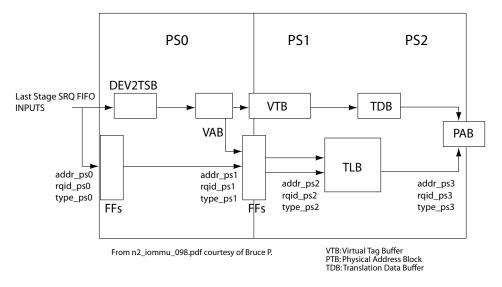

- FIGURE 21-2 IOM Pipeline Diagram 21–3

- FIGURE 21-3 Logical Timing Diagram 21–6

- FIGURE 21-4 Timing Diagram Write 21–7

- FIGURE 21-5 Timing Diagram Read 21–7

- FIGURE 22-1 DMU (128x132) Block Diagram 22–3

- FIGURE 22-2 Internal Operational Diagram 22–4

- FIGURE 22-3 I/O Timing Diagram 22–7

- FIGURE 22-4 Internal Timing, Read 22–8

- FIGURE 22-5 Internal Timing, Write 22–8

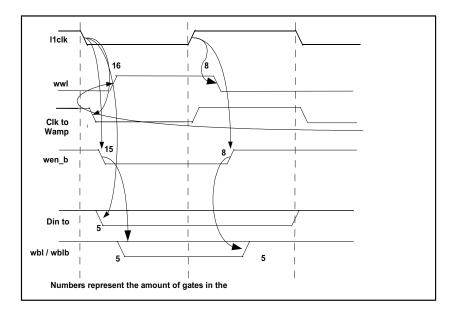

- FIGURE 23-1 DMU (144x149) Block Diagram 23–3

- FIGURE 23-2 Pipeline Diagram 23–4

- FIGURE 23-3 I/O Timing Diagram 23–6

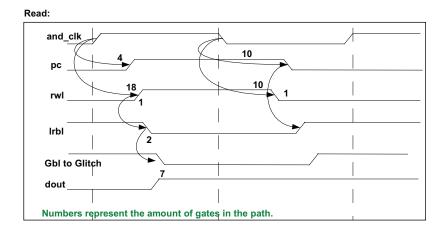

- FIGURE 23-4 Internal Timing, Read 23–7

- FIGURE 23-5 Internal Timing, Write 23–7

- FIGURE 24-1 DMU (512x60) Block Diagram 24–3

- FIGURE 24-2 Internal Operational Diagram 24–4

- FIGURE 24-3 I/O Timing Diagram 24–6

- FIGURE 24-4 Internal Timing, Read 24–6

- FIGURE 24-5 Internal Timing, Write 24–7

- FIGURE 25-1 EFA Block Diagram 25–2

## Tables

- TABLE 1-1

Megacells in the OpenSPARC T2 Processor

1–1

- TABLE 2-1 SCM I/O Signal List 2–6

- TABLE 2-2 SCM Modes of Operation 2–7

- TABLE 3-1TLB I/O Signal List3-6

- TABLE 3-2Primary Control Truth Table3–8

- TABLE 3-3

Output for Primary Operations

3–9

- TABLE 4-1 IRF Functional and DFT I/O Signal List 4–5

- TABLE 4-2 IRF Modes of Operation 4–8

- TABLE 5-1Operations5–3

- TABLE 5-2I/O List5-6

- TABLE 5-3Modes of Operation5–7

- TABLE 5-4Functional Operational Table5–7

- TABLE 6-1Operations6–3

- TABLE 6-2 I/O List 6-5

- TABLE 6-3Modes of Operation6–6

- TABLE 6-4Functional Operational Table6–6

- TABLE 7-1I/O List7-4

- TABLE 7-2 ICD Array Modes of Operation 7–6

- TABLE 7-3

Way Select Decode During Read Operation

7–6

- TABLE 7-4

Way Select Decode During Write Operation

7–7

| TABLE 7-5  | Word Enable During Write Operation 7–8                                |

|------------|-----------------------------------------------------------------------|

| TABLE 8-1  | I/O List 8–4                                                          |

| TABLE 9-1  | I/O List 9–4                                                          |

| TABLE 9-2  | Functional Table 9–6                                                  |

| TABLE 10-1 | DTA I/O List 10–4                                                     |

| TABLE 10-2 | DTA Modes of Operation 10–5                                           |

| TABLE 10-3 | DTA Write Way Select Decode 10–5                                      |

| TABLE 11-1 | DVA I/O List 11–3                                                     |

| TABLE 11-2 | DVA Functional Table 11–5                                             |

| TABLE 12-1 | Functional and Redundancy Repair Related I/O Signal List . 12–4       |

| TABLE 12-2 | Functional Operation Table 12–7                                       |

| TABLE 13-1 | L2 Cache Data Array I/O List 13–5                                     |

| TABLE 13-2 | L2 Cache Data Array Functional Table 13–6                             |

| TABLE 14-1 | Miss Buffer Data Array Functional Input / Output Signal List 14-3     |

| TABLE 14-2 | Miss Buffer Data Array Test Related Signals 14–3                      |

| TABLE 14-3 | Miss Buffer Data Array Operations 14–4                                |

| TABLE 15-1 | Miss Buffer Reauest CAM Pipeline Diagram 15–4                         |

| TABLE 15-2 | Miss Buffer Request CAM I/O List 15–4                                 |

| TABLE 15-3 | Functional Operations 15–5                                            |

| TABLE 16-1 | Instruction Cache and Data Cache Pipeline Diagram 16-6                |

| TABLE 16-2 | Instruction Cache and Data Cache Directory I/O List 16-7              |

| TABLE 16-3 | Instruction Cache and Data Cache Directory Functional Operations 16–8 |

| TABLE 17-1 | Fill Buffer I/O List 17–3                                             |

| TABLE 17-2 | Fill Buffer Pipeline Diagram 17–5                                     |

| TABLE 17-3 | Functional Operations 17–5                                            |

| TABLE 18-1 | Block Instances in L2 18–1                                            |

| TABLE 18-2 | Dual Port Register File (16x160) I/O List 18–4                        |

| TABLE 18-3 | Dual Port Register File (16x160) Modes of Operation 18–5              |

| TABLE 19-1 | Functinal Operation 19–4                                              |

| TABLE 19-2 | I/O Signal List 19–7                                                  |

- TABLE 20-1MCU I/O List20-3

- TABLE 20-2 MCU Functional Operation Table 20–4

- TABLE 21-1IOM I/O List21-4

- TABLE 21-2 Functional Operation 21–5

- TABLE 22-1 I/O List 22–5

- TABLE 22-2 Modes of Operation 22–6

- TABLE 23-1 I/O List 23-4

- TABLE 23-2 Modes of Operation 23–5

- TABLE 24-1DMU I/O List24-4

- TABLE 24-2Modes of Operation24–5

- TABLE 25-1EFA I/O Signal List25–3

# Preface

This document provides information regarding the megacells used in the OpenSPARC<sup>TM</sup> T2 processor, which is the first chip multiprocessor that fully implements the Sun<sup>TM</sup> Throughput Computing Initiative.

## How This Document Is Organized

Chapter 1 provides a summary of all the megacells in the OpenSPARC T2 design.

Chapter 2 describes the Store buffer Content-addressable Memory (SCM), one of two arrays associated with the store buffer of the load and store unit (LSU).

Chapter 3 describes the translation Lookaside Buffer (TLB), commonly used as an Instruction Translation Lookaside Buffer (I-TLB) or a Data Translation Lookaside Buffer (D-TLB) for instruction fetch and for load and store units.

Chapter 4 describes the Integer Register File (IRF), which is a 32-entry x 72-bit structure, replicated four times for each thread.

Chapter 5 describes the Memory Management Unit (MMU).

Chapter 6 describes an 8-Kbit Floating-point Register File (FRF) that contains 128 entries of 64-bit doublewords.

Chapter 7 describes a 16-Kbyte, 32-byte line size, 4-way set-associative Instruction Cache Data (ICD).

Chapter 8 describes a 128-entry, 4-way, set-associative Instruction and Data Cache Tag (ICT).

Chapter 9 describes the 9-Kbyte 4-way set associative Data Cache Array (DCA).

Chapter 10 describes the 9-Kbyte 4-way set associative Data Cache Tag Array (DTA).

Chapter 11 describes the Data Valid Bit array (DVA)..

Chapter 12 describes the 172-Kbyte, 12-way, set-associative Level 2 cache tag array (L2 Tag), which is split into four banks of 43 Kbytes each.

Chapter 13 describes Level 2 cache data array, an inclusive, 3-Mbyte cache composed of four symmetrical banks.

Chapter 14 describes the 32 x 128 Miss Buffer Data Array.

Chapter 15 describes the 32 x 40 Miss Buffer Request CAM.

Chapter 16 describes the 64 x 64 L2- Cache Instruction and Data Directory CAM.

Chapter 17 describes the 8 x 40 L2- Cache Fill Buffer.

Chapter 18 describes the 16 x 160 L2-Cache Dual Port Register File.

Chapter 19 describes the 32 x 160 dL2-Cache VUAD Register File.

Chapter 20 describes the Memory Controller Register File (MCU) 32x72.

Chapter 21 describes the Data Management Unit IOMMU Array.

Chapter 22 describes the Data Management Unit 128 x 132 DMU Register File.

Chapter 23 describes the Data Management Unit 144 x 149 DMU arrray.

Chapter 24 describes the Data Management Unit 512 x 60 DMU Register File.

Chapter 25 describes the Electronic Fuse Array (EFA), composed of an array of 64x32 poly fuses and address decoders.

# Using UNIX Commands

This document might not contain information about basic UNIX<sup>®</sup> commands and procedures such as shutting down the system, booting the system, and configuring devices. Refer to the following for this information:

- Software documentation that you received with your system

- Solaris<sup>TM</sup> Operating System documentation, which is at:

http://docs.sun.com

# Shell Prompts

| Shell                                 | Prompt        |  |

|---------------------------------------|---------------|--|

| C shell                               | machine-name% |  |

| C shell superuser                     | machine-name# |  |

| Bourne shell and Korn shell           | \$            |  |

| Bourne shell and Korn shell superuser | #             |  |

# **Typographic Conventions**

| Typeface*                                                                               | Meaning                                                                                                                     | Examples                                                                                                                                                                         |  |  |

|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| AaBbCc123The names of commands, files,<br>and directories; on-screen<br>computer output |                                                                                                                             | Edit your.login file.<br>Use 1s -a to list all files.<br>% You have mail.                                                                                                        |  |  |

| AaBbCc123                                                                               | What you type, when contrasted% suwith on-screen computer outputPassword:                                                   |                                                                                                                                                                                  |  |  |

| AaBbCc123                                                                               | Book titles, new words or terms,<br>words to be emphasized.<br>Replace command-line variables<br>with real names or values. | Read Chapter 6 in the <i>User's Guide</i> .<br>These are called <i>class</i> options.<br>You <i>must</i> be superuser to do this.<br>To delete a file, type rm <i>filename</i> . |  |  |

\* The settings on your browser might differ from these settings.

# **Related Documentation**

The documents listed as online are available at:

http://www.opensparc.net

| Application   | Title                                                                          | Part Number | Format | Location |

|---------------|--------------------------------------------------------------------------------|-------------|--------|----------|

| Documentation | OpenSPARC T2 Core<br>Microarchitecture Specification                           | 820-2545-11 | PDF    | Online   |

| Documentation | <i>OpenSPARC T2 System-On-Chip</i><br>(SoC) Microarchitecture<br>Specification | 820-2620-11 | PDF    | Online   |

| Documentation | OpenSPARC T2 Processor<br>Megacell Specification                               | 820-2728-10 | PDF    | Online   |

| Documentation | OpenSPARC T2 Processor Design<br>and Verification User's Guide                 | 820-2729-10 | PDF    | Online   |

# Documentation, Support, and Training

| Sun Function  | URL                               |

|---------------|-----------------------------------|

| Documentation | http://www.sun.com/documentation/ |

| Support       | http://www.sun.com/support/       |

| Training      | http://www.sun.com/training/      |

# Third-Party Web Sites

Sun is not responsible for the availability of third-party web sites mentioned in this document. Sun does not endorse and is not responsible or liable for any content, advertising, products, or other materials that are available on or through such sites or resources. Sun will not be responsible or liable for any actual or alleged damage or loss caused by or in connection with the use of or reliance on any such content, goods, or services that are available on or through such sites or resources.

# Sun Welcomes Your Comments

Sun is interested in improving its documentation and welcomes your comments and suggestions. You can submit your comments by going to:

http://www.sun.com/hwdocs/feedback

Please include the title and part number of your document with your feedback:

OpenSPARC T2 Processor Megacell Specification, part number 820-2728-10

CHAPTER 1

# Megacells in the OpenSPARC T2 Processor

This chapter provides a summary of the megacells in the OpenSPARC T2 design. These megacells include various register files, translation lookaside buffers (TLBs), content-addressable memory (CAM), Level 2 cache (L2-cache), and arrays. The following chapters give detailed descriptions of each megacell in the design, including functional descriptions, block diagrams, I/O lists, and timing diagrams.

## 1.1 Overview

TABLE 1-1 lists the megacells in the OpenSPARC T2 design.

TABLE 1-1

Megacells in the OpenSPARC T2 Processor

| Megacell Name         | Chapter No. | Description                              |

|-----------------------|-------------|------------------------------------------|

| n2_stb_cm_64x45_cust  | 2           | Store Buffer CAM (SCM)                   |

| n2_tlb_tl_128x59_cust | 3           | Translation Lookaside Buffer (TLB)       |

| n2_irf_mp_128x72_cust | 4           | Integer Register File (IRF)              |

| n2_mmu_cm_64x34s_cust | 5           | Memory Management Unit CAM (MMU)         |

| n2_frf_mp_256x78_cust | 6           | Floating-point register file (FRF)       |

| n2_icd_sp_16p5kb_cust | 7           | Instruction Cache (I\$) Data Array (ICD) |

| n2_ict_sp_1920b_cust  | 8           | Instruction Cache Tag Array (ICT)        |

| n2_dca_sp_9kb_cust    | 9           | Data Cache Array (DCA)                   |

| n2_dta_sp_1920b_cust  | 10          | Data Cache Tag Array (DTA)               |

| n2_dva_dp_32x32_cust  | 11          | Data Valid Bit Array (DVA)               |

| Megacell Name             | Chapter No. | Description                                 |

|---------------------------|-------------|---------------------------------------------|

| n2_l2t_sp_28kb_cust       | 12          | L2-Cache Tag Array                          |

| n2_l2d_sp_512kb_cust      | 13          | L2-Cache Data Array                         |

| n2_l2t_dp_32x128_cust     | 14          | L2-Cache Miss Buffer Data Array             |

| n2_com_cm_32x40_cust      | 15          | L2-Cache Miss Buffer Request CAM            |

| n2_com_cm_64x64_cust      | 16          | L2-Cache Instruction and Data Directory CAM |

| n2_com_cm_8x40_cust       | 17          | L2-Cache Fill Buffer                        |

| n2_l2t_dp_16x160_cust     | 18          | L2-Cache Dual Port Register File            |

| n2_l2t_dp_32x160_cust     | 19          | L2-Cache VUAD Register File                 |

| n2_mcu_32x72async_dp_cust | 20          | Memory Controller Register File             |

| n2_iom_sp_devtsb_cust     | 21          | Data Management Unit IOMMU Array            |

| n2_dmu_dp_128x132s_cust   | 22          | Data Management Unit 128x132 RegisterFile   |

| n2_dmu_dp_144x149s_cust   | 23          | Data Management Unit 144x149 Array          |

| n2_dmu_dp_512x60s_cust    | 24          | Data Management Unit 512x60 RegisterFile    |

| n2_efa_sp_256b_cust       | 25          | e-Fuse                                      |

TABLE 1-1

Megacells in the OpenSPARC T2 Processor (Continued)

# Store Buffer CAM (SCM)

This chapter describes the following topics:

- Functional Description

- Block Diagram

- Pipeline Diagram

- I/O List

- Timing Diagram

# 2.1 Functional Description

### 2.1.1 General

- The Store Buffer CAM (SCM) stores the address of each pending store of the load/store unit. All loads check for an address match to see if a Read After Write (RAW) hazard occurs.

- The SCM contains 64 logical entries. This is logically divided into 8 groups (each group for a different thread) each containing 8 entries. In a lookup cycle, the CAM thread id input bus will select only one of the 8 groups.

- Each entry contains 37 bits of tag (stored address), and 8 bits of byte-mask which indicate which of the 8 bytes are actually going to be stored into memory.

- All 45 (37 tag + 8 byte-mask) of the bits in each entry are capable of being written to and read from the SCM array.

- There is 1 read and 1 write port which both share the same address input, and a CAM (lookup) port.

- A read and lookup operation are allowed to occur in the same cycle, but all other combinations are not allowed.

- Any access can occur in consecutive clock cycles.

## 2.1.2 Lookup Operation

- For the lookup operation, the 37 bits of tag in every entry are compared against the compare input bus (aka "key"). If at least one of the 8 byte-mask bits is set to '1' in both the entry and the key, then this is considered a "byte\_match". The result of the tag compare and the byte\_match results are then ANDed together. Finally these results are ANDed with the line-enables of the corresponding entries to get the CAM-hit results.

- The CAM-hit result is decoded into a 3 bit address indicating which logical entry (out of the 8 entries in the "thread group") had a hit.

- The final CAM-hit signal for the block is the OR of the CAM-hits of all the entries.

- If an entry has a CAM-hit, and there is at least one bit of it's byte-mask which is set to a '0' while the corresponding bit of the byte-mask key is set to '1', then this is considered a partial hit. The partial output signal is activated in this case.

- If more than one entry has a CAM-hit, then the multi-hit output signal is activated. In this case, the output hit address and partial output signals are meaningless.

- The CAM lookup occurs in phase 1. This is flopped outside of the block.

- In 16 byte loads, the LSB of the tag compare needs to be masked. This is controlled by the quad\_ld\_cam input.

### 2.1.3 Read Operation

- Read cycle is a single cycle, and occurs in phase 1.

- During a read cycle, all 37 bits of tag and 8 bits of byte-mask are read, flopped and sent to the output bus.

### 2.1.4 Write Operation

- Write cycle is a single cycle, and occurs in phase 1.

- 37 bits of tag and 8 bits of byte-mask are provided to the block to be written, and are setup to the rising edge of clock.

# 2.2 Block Diagram

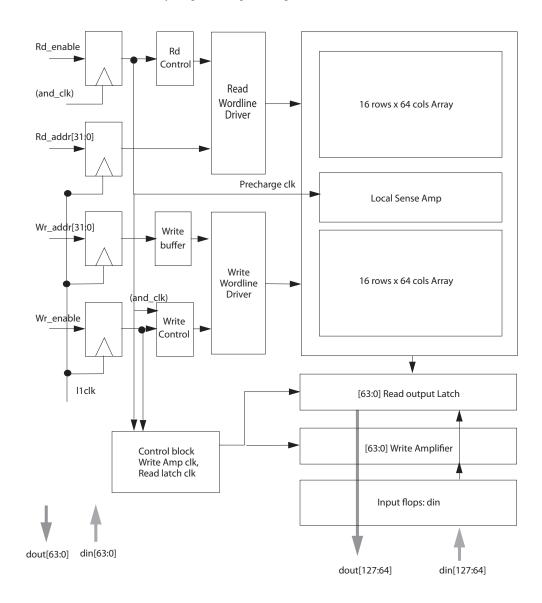

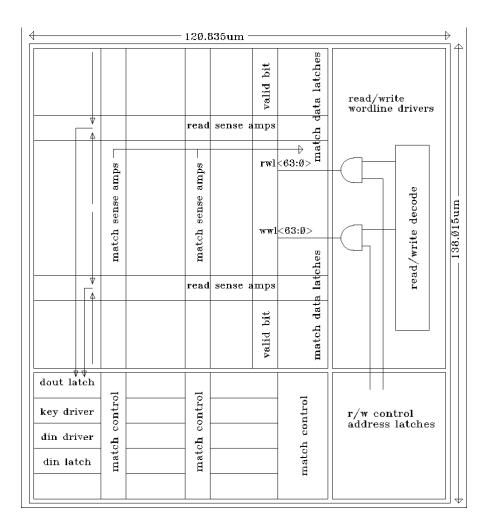

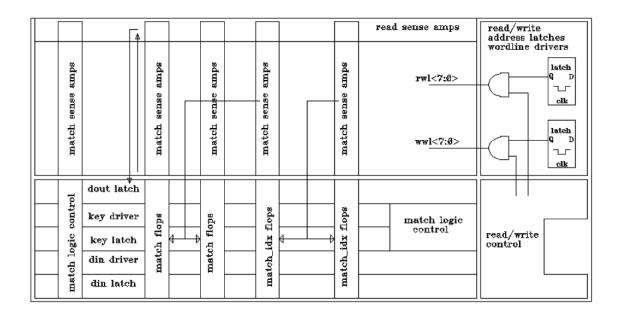

### FIGURE 2-1 SCM Block Diagram

- There will be 2 physical banks of arrays. The left array will contain the 64 rows by 8 bits of byte-mask, and the right array will contain the 64 rows by 37 bits of tag. Any 8 threads of the same entry will be physically next to each other.

- There will be dummy rows above and below each portion of 16 entries.

- There will be 2 dummy edge columns at the left and right side of the tag array. There will also be 2 dummy edge columns at the left and right side of the bytemask array.

# 2.3 Pipeline Diagram

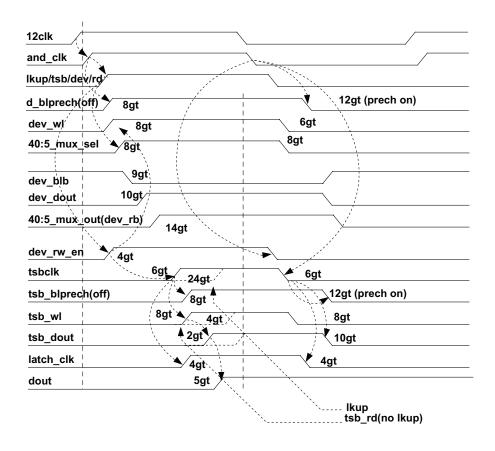

FIGURE 2-2 SCM Pipeline Diagram

address, read enable, write enable, cam enable, and data inputs are flopped

# 2.4 I/O List

The following table describes the SCM I/O signals.

| Signal Name               | Width  | I/O | Flopped | Source/Deal | Description                                         |

|---------------------------|--------|-----|---------|-------------|-----------------------------------------------------|

| stb_cam_rw_ptr            | [2:0]  | IN  | Yes     | lsu_sbc_ctl | Read/write address                                  |

| stb_cam_rw_tid            | [2:0]  | IN  | Yes     | lsu_sbc_ctl | Thread ID for read/write                            |

| stb_cam_wptr_vld          |        | IN  | Yes     | lsu_sbc_ctl | Write enable                                        |

| stb_cam_rptr_vld          |        | IN  | Yes     | lsu_sbc_ctl | Read enable                                         |

| stb_cam_vld               |        | IN  | Yes     |             | Lookup enable                                       |

| stb_cam_cm_tid            | [2:0]  | IN  | Yes     |             | Thread ID for Lookup operation                      |

| stb_cam_line_en           | [7:0]  | IN  | No      |             | Line enables for Lookup results                     |

| stb_quad_ld_cam           |        | IN  | Yes     |             | Masks LSB of tag in a lookup (for<br>16 byte loads) |

| stb_camwr_data            | [44:0] | IN  | Yes     |             | Data for compare/write                              |

| stb_rdata_ramc            | [44:0] | OUT | Yes     |             | Read data                                           |

| stb_ld_partial_raw        |        | OUT | No      |             | Partial Lookup Result                               |

| stb_cam_hit_ptr           | [2:0]  | OUT | No      |             | Address location of matched entry                   |

| stb_cam_hit               |        | OUT | No      |             | Store buffer hit                                    |

| stb_cam_mhit              |        | OUT | No      |             | Multiple hit                                        |

| Clock and Test Related I/ | 0      |     |         |             |                                                     |

| l2clk                     |        | IN  | No      | clock grid  | L2 clock input                                      |

| scan_in                   |        | IN  | No      |             | Scan input                                          |

| tcu_pce_ov                |        | IN  | No      | tcu         | Test controller input                               |

| tcu_aclk                  |        | IN  | No      | tcu         | Test controller scan-in clock                       |

| tcu_bclk                  |        | IN  | No      | tcu         | Test controller scan-out clock                      |

| рсе                       |        | IN  | No      | tied high   | Clock enable.                                       |

| tcu_array_wr_inhibit      |        | IN  | No      | tcu         | Disables writes during test modes                   |

| tcu_se_scancollar_in      |        | IN  | No      | tcu         | Scan-enable for input flops/latches                 |

| TABLE 2-1 | SCM I/O Signal List |

|-----------|---------------------|

|-----------|---------------------|

| Signal Name           | Width | I/O | Flopped | Source/Deal | Description                       |

|-----------------------|-------|-----|---------|-------------|-----------------------------------|

| tcu_se_scancollar_out |       | IN  | No      | tcu         | Scan-enable for output flops      |

| tcu_scan_en           |       | IN  | No      | tcu         | Scan-enable for internal clocking |

| scan_out              |       | OUT | No      |             | Scan output                       |

### TABLE 2-1 SCM I/O Signal List (Continued)

# 2.4.1 Modes of Operation

| Enable Values |       | lues   |                                                                                                 | Output Results        |                   |                  |         |          |

|---------------|-------|--------|-------------------------------------------------------------------------------------------------|-----------------------|-------------------|------------------|---------|----------|

| read          | write | lookup | Memory Operation                                                                                | ramc<br><44:0>        | partial           | hit_ptr<br><2:0> | cam_hit | cam_mhit |

| 1             | 0     | 0      | Read Cycle                                                                                      | results<br>of<br>read | 0                 | 0                | 0       | 0        |

| 0             | 1     | 0      | Write Cycle                                                                                     | 0                     | 0                 | 0                | 0       | 0        |

| 0             | 0     | 1      | Lookup Cycle                                                                                    | 0                     | results of lookup |                  |         |          |

| 1             | 0     | 1      | Read and Lookup Cycle                                                                           | results<br>of<br>read | results of lookup |                  |         |          |

| 0             | 0     | 0      | No Operation                                                                                    | 0                     | 0                 | 0                | 0       | 0        |

| 1             | 1     | 0      | Monitors in RTL do not allow these scenarios. Memory contents and outputs may be indeterminate. |                       |                   |                  |         |          |

| 0             | 1     | 1      |                                                                                                 |                       |                   |                  |         |          |

| 1             | 1     | 1      |                                                                                                 |                       |                   |                  |         |          |

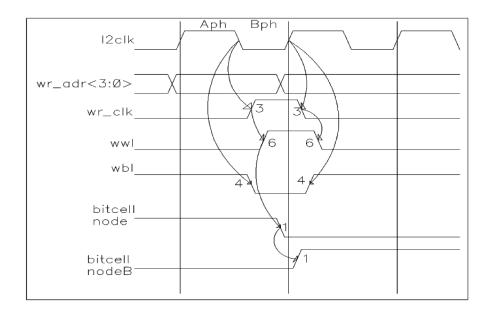

# 2.5 Timing Diagram

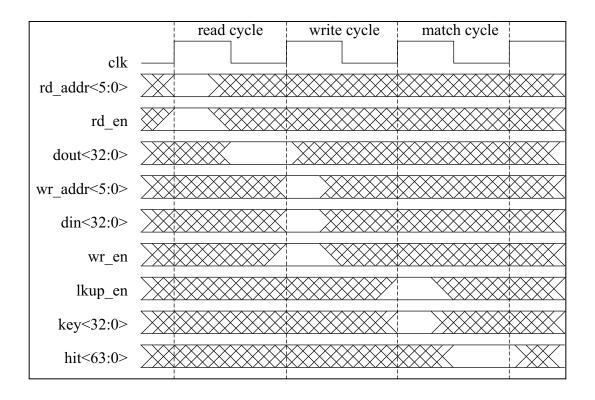

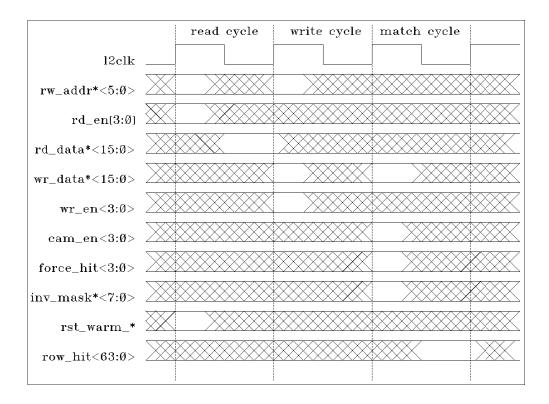

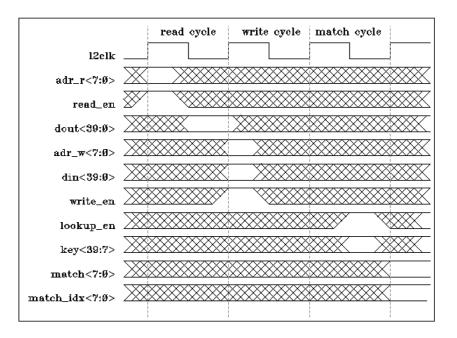

### FIGURE 2-3 SCM Timing Diagram

# Translation Lookaside Buffer (TLB)

This chapter describes the following topics:

- Functional Description

- DTLB Description

- ITLB Description

- I/O List

# 3.1 Functional Description

In today's computers most programs running on a machine assume that they have the entire memory of the system to themselves. These programs utilize a virtual memory abstraction which requires that the virtual addresses must be converted to real, physical addresses before the physical memory can be actually accessed. The virtual to physical address translation is performed in the CPU by the Translation Lookaside Buffer (TLB). The TLB does not map individual memory locations but instead maps larger regions of memory (pages). In the following paragraphs a description of the Data TLB (DTLB) and Instruction TLB (ITLB) supported on OpenSPARC T2 and its enhancements and differences with respect to its first generation implementation are provided.

### 3.1.1 OpenSPARC T1 vs OpenSPARC T2

OpenSPARC T2 has a 128-entry Data TLB (DTLB), while OpenSPARC T1 has a 64entry DTLB. The Instruction TLB (ITLB) is 64-entry and remains the same.

- The instruction cache is 8-way set associative in OpenSPARC T2 as compared to 4-way in OpenSPARC T1. Hence, 8 cache ptag comparators are required in the ITLB. The data cache is 4-way set associative in OpenSPARC T2. Hence, 4 cache ptag comparators are required in DTLB.

- OpenSPARC T2 supports a pair of primary context registers and a pair of secondary context registers. OpenSPARC T1 supports a single primary context and single secondary context register. Multiple primary and secondary contexts permit different processes to share TTEs within the TLBs. To maintain backwards compatibility with software designed for a single primary and single secondary context register (OpenSPARC T1, writes to primary (secondary) context 0 register also update primary (secondary) context 1 register.

- OpenSPARC T2 does not support a locked bit in the TLBs. OpenSPARC T1 supports a locked bit in the TLBs.

- OpenSPARC T1 and OpenSPARC T2 support the same four page sizes (8 kB, 64 kB, 4 MB, 256 MB).

- OpenSPARC T2 adds a demap real operation, which demaps all pages with R=1 from the TLB.

- Autodemapping of pages in the TLBs only demaps pages of the same size or of a larger size in OpenSPARC T2. In OpenSPARC T1, autodemap demaps pages of the same size, larger size, or smaller size.

- OpenSPARC T1 and OpenSPARC T2 use the same used bit-based pseudo-LRU TLB replacement scheme.

- OpenSPARC T2 supports detection of multiple hits in the TLBs.

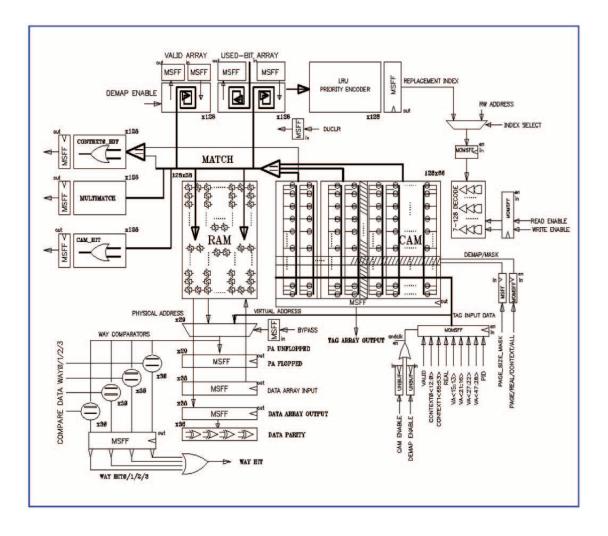

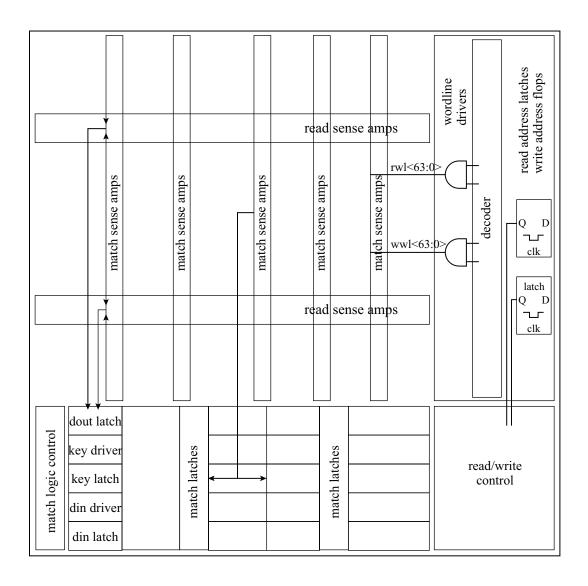

## 3.1.2 DTLB Description

- The DTLB is divided into a tag array (128x66 entries) and a data array (128x38 entries)

- The DTLB has a separate Used bit array, Valid bit array and Real bit array.

- The DTLB has a 128-bit multi-match detect & priority encoder and 4-way comparators.

- Clock headers are distributed along the width of the block.

## 3.1.3 ITLB Description

- The ITLB is divided into a tag array (64x66 entries) and a data array (64x38 entries)

- The ITLB has a separate Used bit array, Valid bit array and Real bit array.

- The ITLB has a 64-bit multi-match detect & priority encoder and 8-way comparators.

- Clock headers are distributed along the width.

## 3.2 Block Diagrams

#### FIGURE 3-1 DTLB Block Diagram

# 3.3 I/O List

The following table describes the TLB I/O signals.

| IADLE 3-1 ILD I/ O Signal LIS | TABLE 3-1 | TLB I/O Signal List |

|-------------------------------|-----------|---------------------|

|-------------------------------|-----------|---------------------|

| Port Name      | Туре   | UN/FF/LAT   | Width | Function                             |  |  |

|----------------|--------|-------------|-------|--------------------------------------|--|--|

|                |        | ADD         | RESS  |                                      |  |  |

| tlb_rw_index   | input  | flopped     | 7     | read/write address (DTLB)            |  |  |

| tlb_rw_index   | input  | flopped     | 6     | read/write address (ITLB)            |  |  |

|                | 1      | D           | АТА   |                                      |  |  |

| tte_tag        | input  | flopped/NAN | 66    | D/I TLB tag array write/compare data |  |  |

| tte_data       | input  | flopped     | 38    | D/I TLB data arraywrite data         |  |  |

| tlb_tte_tag    | output | flopped     | 66    | D/I TLB tag array read data          |  |  |

| tlb_tte_data   | output | flopped     | 38    | D/I TLB data array read data         |  |  |

| tte_ubit       | input  | flopped     | 1     | D/I TLB used bit                     |  |  |

| tlb_tte_u_bit  | output | flopped     | 1     | D/I TLB used bit                     |  |  |

| tlb_va         | input  | flopped     | 2     | D/I TLB incoming virtual address     |  |  |

| tlb_pgnum      | output | flopped     | 27    | D/I TLB physical address             |  |  |

| tlb_pgnum_crit | output | unflopped   | 27    | D/I TLB physicall address            |  |  |

#### CACHE TAG COMPARE DATA

| cache_ptag_w0 | input | unflopped      | 30    | D/I TLB Way 0 compare data |

|---------------|-------|----------------|-------|----------------------------|

| cache_ptag_w1 | input | unflopped      | 30    | D/I TLB Way 1 compare data |

| cache_ptag_w2 | input | unflopped 30 D |       | D/I TLB Way 2 compare data |

| cache_ptag_w3 | input | unflopped      | 30    | D/I TLB Way 3 compare data |

| cache_ptag_w4 | input | unflopped      | 30    | ITLB Way 4 compare data    |

| cache_ptag_w5 | input | unflopped      | 30    | ITLB Way 5 compare data    |

| cache_ptag_w6 | input | unflopped      | 30    | ITLB Way 6 compare data    |

|               |       | CO             | NTROL |                            |

| tlb_cam_vld   | input | flopped/NAN    | 1     | D/I TLB compare enable     |

| tlb_demap     | input | flopped/NAN    | 1     | D/I TLB demap enable       |

| Port Name            | Туре   | UN/FF/LAT       | Width      | Function                             |

|----------------------|--------|-----------------|------------|--------------------------------------|

| tlb_demap_context    | input  | flopped         | 1          | D/I TLB demap context enable         |

| tlb_demap_all        | input  | flopped         | 1          | D/I TL:B demap all enable            |

| tlb_demap_real       | input  | flopped         | 1          | D/I TL:B demap real enable           |

| tlb_demap_page       | input  | flopped         | 1          | D/I TLB demap page enable            |

| tlb_wr_vld           | input  | flopped/NAN     | 1          | D/I TLB write enable                 |

| tlb_rd_vld           | input  | flopped/NAN 1 D |            | D/I TLB read enable                  |

| tlb_bypass           | input  | flopped         | 1          | D/I TLB bypass enable                |

| disable_clear_ubit   | input  | flopped         | 1          | D/I TLB disable U-bit clearing       |

| tlb_rw_index_vld     | input  | flopped/NAN     | 1          | D/I TLB regular/replacement select   |

| tte_page_size_mask   | input  | flopped         | 1          | D/I TLB page mask during write       |

|                      |        | MISCELLANI      | EOUS SIGNA | LS                                   |

| cache_set_vld        | input  | unflopped       | 4          | D/I TLB compare enable               |

| cache_way_hit        | output | flopped         | 4          | D/I TLB demap enable                 |

| cache_hit            | output | ff (delayed)    | 1          | D/I TLB demap context enable         |

| tlb_cam_hit          | output | flopped         | 1          | D/I TLB 128-bit OR; compare hit      |

| tlb_context0_hit     | output | flopped         | 1          | D/I TLB 128-bit OR; context0 hit     |

| tlb_tte_data_parity  | output | ff (delayed)    | 1          | D/I TLB data array parity            |

|                      |        | CLOCK RELA      | TED CONTRO | DLS                                  |

| l2clk                | input  | x               | 1          | D/I TLB global clock                 |

| scan_in              | input  | x               | 1          | D/I TLB scan input                   |

| scan_out             | output | x               | 1          | D/I TLB scan output                  |

| tcu_aclk             | input  | x               | 1          | D/I TLB a-phase scan input clock     |

| tcu_bclk             | input  | x               | 1          | D/I TLB b-phase scan input clock     |

| tcu_se_scancollar_in | input  | x               | 1          | D/I TLB input clock header control   |

| tcu_se_scancollar_ou | input  | x               | 1          | D/I TLB output clock header control  |

| tcu_array_wr_inhibit | input  | x               | 1          | D/I TLB write inhibit                |

| tcu_clk_stop         | input  | x               | 1          | D/I TLB disable clock header control |

| tcu_pce_ov           | input  | x               | 1          | D/ITLB test controller input         |

TABLE 3-1

TLB I/O Signal List (Continued)

#### 3.3.1 IDTLB/ITLB Modes of Operation

The TLB supports the following operations per clock cycle:

#### 3.3.1.1 Primary Operations

- Read (tlb\_rd\_vld)

- Compare (tlb\_cam\_vld)

- Write (tlb\_wr\_vld)

- Demap Page (tlb\_demap)

- Demap Context (tlb\_demap & tlb\_demap\_context)

- Demap Real (tlb\_demap & tlb\_demap\_real)

- Demap All (tlb\_demap & tlb\_demap\_all)

- Bypass (tlb\_bypass)

#### 3.3.1.2 Secondary Operations

- Used Bit Setting

- Used Bit Resetting

- Replacement Index (Valid | Used) generation

- Valid Bit Resetting

- Replacement Index Write (Feedback Loop)

- Array Write Inhibit

- Multimatch Generation

- Context0 Hit Generation

- Data Parity

- TLB Cam Hit)

| oper  | rw_idx | rd | wr | cam | dm<br>p | dmpal | dmpcx | dmprl | byp | duclr | wr_ih | msk | V   | R   | U   |

|-------|--------|----|----|-----|---------|-------|-------|-------|-----|-------|-------|-----|-----|-----|-----|

| noop  | 1/0    | 0  | 0  | 0   | 0       | 0     | 0     | 0     | 0   | 0     | 1/0   | 0   | 0   | 0   | 0   |

| read  | 1      | 1  | 0  | 0   | 0       | 0     | 0     | 0     | 0   | x     | 1/0   | x   | 1/0 | 1/0 | 1/0 |

| write | 1/0    | 0  | 1  | 0   | 0       | 0     | 0     | 0     | 0   | 1/0   | 1/0   | 1/0 | 1/0 | 1/0 | 1/0 |

| cam   | 1/0    | 0  | 0  | 1   | 0       | 0     | 0     | 0     | 0   | 1/0   | 1/0   | x   | 1/0 | 1/0 | 1/0 |

| dmppg | 1/0    | 0  | 0  | 0   | 1       | 0     | 0     | 0     | 0   | x     | 1/0   | x   | 1/0 | 1/0 | 1/0 |

#### TABLE 3-2 Primary Control Truth Table

| dmpal  | 1/0 | 0 | 0 | 0   | 1 | 1 | 0 | 0 | 0 | x | 1/0 | x | 1/0 | 1/0 | 1/0 |

|--------|-----|---|---|-----|---|---|---|---|---|---|-----|---|-----|-----|-----|

| dmpcx  | 1/0 | 0 | 0 | 0   | 1 | 0 | 1 | 0 | 0 | х | 1/0 | x | 1/0 | 1/0 | 1/0 |

| dmprl  | 1/0 | 0 | 0 | 0   | 1 | 0 | 0 | 1 | 0 | х | 1/0 | x | 1/0 | 1/0 | 1/0 |

| bypass | 1/0 | 0 | 0 | 1/0 | 0 | 0 | 0 | 0 | 1 | 0 | 1/0 | x | 1/0 | 1/0 | 1/0 |

TABLE 3-2

Primary Control Truth Table (Continued)

**Note** – All controls are gated by *tcu\_array\_wr\_inihibit* except cam\_hit output flop

| oper   | pgcrit | pgnum | \$hit | \$whit | mhit | c0hit | camhit | dataout | tagout | prty | ubit | vld |

|--------|--------|-------|-------|--------|------|-------|--------|---------|--------|------|------|-----|

| noop   | x0     | x0    | 1/0   | 1/0    | x0   | x0    | x0     | x0      | x0     | 0    | x    | x   |

| read   | 1/0    | 1/0   | 1/0   | 1/0    | 0    | 0     | 0      | 1/0     | 1/0    | 1/0  | 1/0  | 1/0 |

| write  | 0      | 0     | 1/0   | 0      | x0   | x0    | x0     | x0      | x0     | 0    | 1/0  | 1/0 |

| cam    | 1/0    | 1/0   | 1/0   | 1/0    | 1/0  | 1/0   | 1/0    | 1/0     | x0     | 1/0  | 1/0  | x   |

| dmppg  | x0     | x0    | 1/0   | 1/0    | x0   | 1/0   | x0     | x0      | x0     | 0    | x    | 0   |

| dmpal  | x0     | x0    | 1/0   | 1/0    | x0   | 1/0   | x0     | x0      | x0     | 0    | x    | 0   |

| dmpcx  | x0     | x0    | 1/0   | 1/0    | x0   | 1/0   | x0     | x0      | x0     | 0    | x    | 0   |

| dmprl  | x0     | x0    | 1/0   | 1/0    | x0   | 1/0   | x0     | x0      | x0     | 0    | x    | 0   |

| oypass | 1/0    | 1/0   | 1/0   | 1/0    | 0    | 0     | 1      | x0      | x0     | 0    | x    | x   |

TABLE 3-3

Output for Primary Operations

**Note** – x : unaffected; x0 : unaffected and default state 0

- Normal Translation: The TLB receives a virtual address and a context identifier as input and produces a physical address and page attributes as output. This operation is contolled by tlb\_cam\_vld. This is a single cycle operation resulting in the generation of the physical address and individual way hit.

- Read Operation: The TLB simultaneously reads the CAM and RAM portion of the specified entry. This operation is controlled by tlb\_rd\_vld and tlb\_rw\_index\_vld (=1 regular index; =0 replacement index). This a single cycle operation with the tag array accessed during the A-phase and the data array accessed during the B-phase.

- Write Operation: The TLB simultaneously writes the CAM and RAM portion of the specified entry, or the entry given by the replacement policy. This operation is controlled by tlb\_wr\_vld and tlb\_rw\_index\_vld (=1 regular index; =0 replacement index). This a single cycle operation with the tag array accessed during the Aphase and the data array accessed during the B-phase.

- Bypass Operation: The TLB receives a virtual address as input and produces a physical address equal to the truncated virtual address page attributes as output. This operation is controlled by tlb\_bypass.

- Demap Operation: The TLB receives a virtual address and a context identifier as input and sets the valid bit to zero for any entry matching the demap page or demap context or demap real or demap all criteria. This operation produces no output.

The purpose of a demap operation is to remove zero, one, or more entries in the TLB. Four types of demap operations are provided: context, real, page and all. The 3bit partition identifier is compared in all demap operations. All these operations alongwith their implementation have been shown in the tag array datatpath organization.

- Demap Page (Type 0 demap operation) removes the TTE from the specified TLB matching the specified virtual page number, real bit, partition identifier register, and context register. Virtual page offset bits <15:13>, <21:13> and <27:13> for 64 kB, 4 MB, and 256 MB page TLB entries, respectively, are stored in the TLB, but are always set to zero and do not participate in the match for that entry. This is the same condition as for a translation match. This operation is controlled by tlb\_demap.

- Demap Context (Type 1 demap operation) removes all TTEs from the specified TLB having the specified context, a real bit of 1'b0 and matching the partition identifer register. This operation is controlled by tlb\_demap and tlb\_demap\_context.

- Demap All (Type 2 demap operation) removes all TTEs from the specified TLB matching the partition identifier register. This operation is controlled by tlb\_demap and tlb\_demap\_all.

- Demap Real (Type 3 demap operation) removes all TTEs from the specified TLB matching the specified real bit and the partition identifier register. This operation is controlled by tlb\_demap and tlb\_demap\_real.

Replacement Policy: OpenSPARC T2 uses a 1-bit LRU scheme. Each TLB entry has an associated valid and used bit. Used bits are set on each TLB translation and also on the initial TLB write of an entry. When setting the used bit for a translation or TLB write would result in all used bits being set, the used bits for all TLB entries are cleared instead. This is a 2-cycle operation.

## 3.4 Timing Diagrams

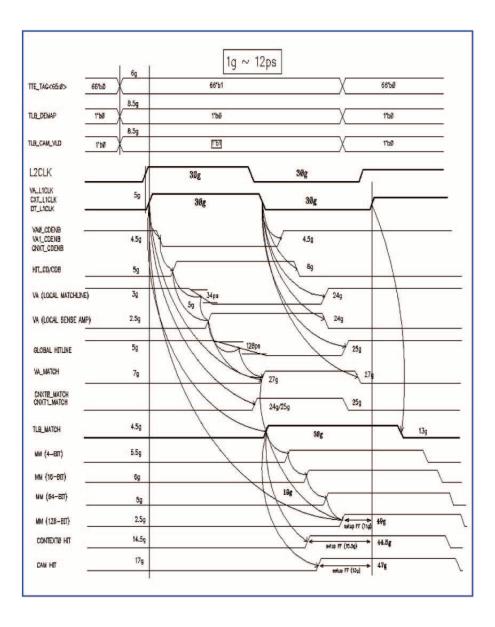

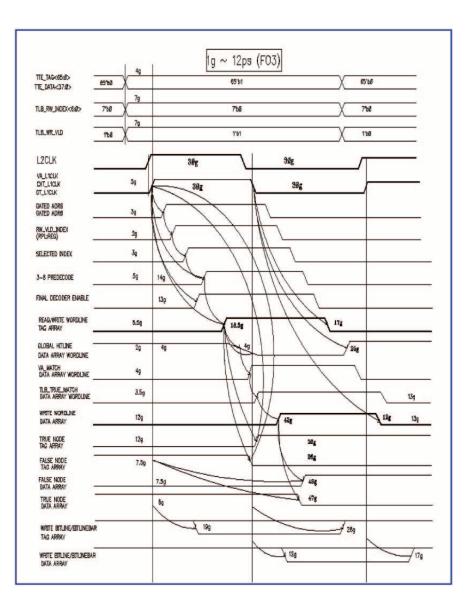

FIGURE 3-3 I/O Timing Diagrams (CAM

FIGURE 3-4 I/O Timing Diagrams (Demap)

FIGURE 3-5 I/O Timing Diagrams (Replacement Index)

FIGURE 3-7 I/O Timing Diagrams (Write)

### Integer Register File (IRF)

This chapter describes the following topics:

- Functional Description

- Block Diagram

- I/O List

- Functional Operation

- Timing Diagram

### 4.1 Functional Description

The integer register file (IRF) is a 32-entry x 72-bit structure, replicated four times for each thread. It has three read ports and two write ports. All three reads occur to the same thread, while the writes may be to different threads.

The first write port is for data from the normal integer pipeline or loads that do not return as long-latency operations. The second write port is for data from longlatency operations (load, division, multiplication). Because a load will always get access, no acknowledgement is required. However, both the multiplication (MUL) and division (DIV) require acknowledgements and will stall until their data has been written.

The 32 entries are split into 16 I/O registers – eight local registers and eight global registers. The register file supports eight windows per thread. Each local register is made up of eight basic registers, one per window. In addition, they contain one active register for each thread, which has the contents of the current window. Each I/O register has four basic registers, which will be shared between even and odd windows, and one active register for each thread.

A SWAP operation involves both SAVE and RESTORE operations pipelined internally and takes three cycles. A SWAP of locals, globals, evens, or odds can occur. However, only two SWAPs out of four sets of registers will occur due to power constraints.

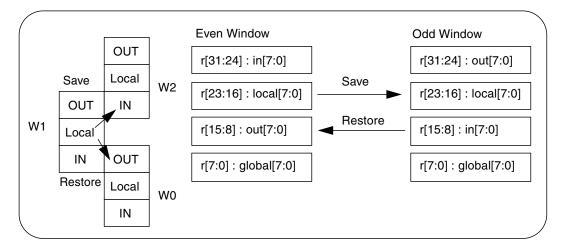

A SAVE is done by transferring the contents of the active register to one of the basic registers attached to it. Later when a RESTORE is done, the contents of this basic register are transferred back to the active register. The "in" register in an odd window becomes the "out" register in an even window and vice versa. Input register addresses must be translated to real register addresses before they are sent to the register file as shown in FIGURE 4-1. In an even window, the input and real address are the same. In the odd window, address range [31:24] must be translated to [15:8], and the address range [15:8] will be translated to [31:24]. The global registers are the same across all windows. They are replicated to provide three sets of alternate global registers for use by privileged software only.

#### 4.1.1 General

Integer Register File functions include the following:

- 1.4Ghz read and write, based on simulation with spl\_noise netlist.

- Three single ended read ports Two dual ended write ports.

- Data width is 72 bits. Array uses 2 -> 1 column mux.

- 32 active registers for each type : even, local, odd, and global.

- Even, odd, and global have four shadow registers for each active register.

- Local has eight shadow registers for each active register.

- Write to active reg in 2nd phase. Read/Save/Restore to active reg in 1st phase.

- Read/Write is a single cycle operation. Save/Restore is a two cycle operation.

- Multiple Writes to same address (tid) disallowed via external logic

- Read/Write to same address produces "X" on output.

- Both Save and Restore to same thread in same cycle disallowed via external logic.

- Save/Restore allowed in all 4 reg types (even, odd, local, global) at same time.

- Flop bound inputs. No flops for Dout.

- All BIST external to array.

- Library flops with custom layout used on inputs.

- Custom non-scanable latches for swap wordline cntrl between 1st and 2nd cycle.

### 4.1.2 Read/Write Operations

- Data width is 72 bits. Array uses 2 -> 1 column mux.

- Write to active reg in 2nd phase. Read to active reg in 1st phase.

- Read/Write is a single cycle operation.

- Multiple Writes to same address (tid) disallowed via external logic

- Read/Write to same address produces "X" on output.

### 4.1.3 Save/Restore Operations

- 32 active registers for each type : even, local, odd, and global.

- Even, odd, and global have four shadow registers for each active register.

- Local has eight shadow registers for each active register.

- Save/Restore to active reg in 1st phase.

- Save/Restore is a two cycle operation.

- Both Save and Restore to same thread in same cycle disallowed via external logic.

- Save/Restore allowed in all 4 reg types (even, odd, local, global) at same time.

### 4.1.4 Illegal Operations

Read and Write to the same TID and same address in the same cycle allowed. Write will complete. Read will produce an 'X' in RTL and possible high power state via metastability. (read collision)

- Both write ports can not write to the same TID in the same cycle. (write collision)

- Save and Restore to the same TID in the same cycle not allowed. (swap collision)

- No phases with back to back operations to the same TID. No swaps immediately preceeded or followed by a read or write to the same TID. (access overlap)

## 4.2 Block Diagram

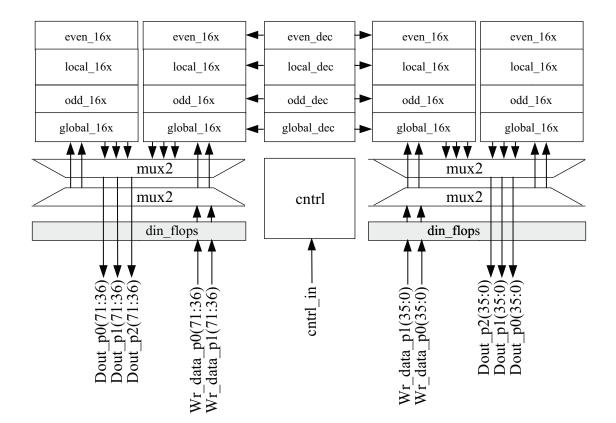

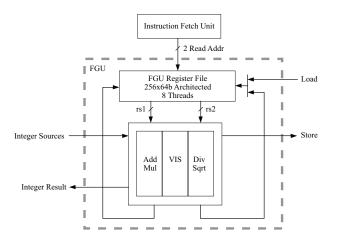

The OpenSPARC T2 processor has eight  ${\rm SPARC}^{\circledast}$  cores. IRF is part of each SPARC core.

FIGURE 4-2 IRF Block Diagram

# 4.3 I/O List

In the following IRF I/O list, all timing is with regard to rclk.

- Signal naming is source\_destination\_signalname.

- *ifu* is instruction fetch unit.

- *ecl* is exu control logic.

- *byp* is bypass unit.

- *rml* is register management.

- *logic, clk, si, so, se* are global signals.

- -12 r means 12 ps setup with regard to rclk clock.

- rclk(L2clk) 12 f means -12 ps setup with regard to falling clock.

- rclk(L2clk) Output delay is with regard to falling rclk with 4x o/p load.

TABLE 4-1

IRF Functional and DFT I/O Signal List

| Name             | Width | I/O | Flopped | Source/<br>Dest | Function                                                                                                                                                                                                                                                                                        |

|------------------|-------|-----|---------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| dout_p[2/1/0]    | 72    | 0   |         |                 | Data to be read on port[2/1/0]                                                                                                                                                                                                                                                                  |

| rd_addr_p[2/1/0] | 5     | Ι   | Y       |                 | Determines which entry is read on port[2/1/0].<br>Bits(4:1) are used to index into one of sixteen<br>wordlines. Decodes of 0-3 access global registers, 4-<br>7 odd registers, 8-11 local registers, and 12-15 even<br>registers. Bit(0)is used for mux2 selection of 72 out<br>of 144 columns. |

| rd_en_p[2/1/0]   | 1     | Ι   | Y       |                 | Enables a specific port for reading.                                                                                                                                                                                                                                                            |

| rd_tid           | 2     | Ι   | Y       |                 | Determines which thread is made available to the<br>read port. All ports see the same tid selection for<br>reads                                                                                                                                                                                |

| wr_data_p[1/0]   | 72    | Ι   | Y       |                 | Data to be written on $port[1/0]$ . All BIST muxing external.                                                                                                                                                                                                                                   |

| wr_addr_p[1/0]   | 5     | I   | Y       |                 | Determines which entry is written on port[1/0].<br>Bits(4:1) are used in conjunction with the<br>wr_tid_p[1/0] bits for that specific port to index into<br>one of sixty-four wordlines. Bit(0) is used for mux2<br>selection of 72 out of 144 columns.                                         |

| wr_en_p[1/0]     | 1     | Ι   | Y       |                 | Enables a specific port for writing.                                                                                                                                                                                                                                                            |

| TABLE 4-1 | IRF Functional and | DFT I/O Signal | List (Continued) |

|-----------|--------------------|----------------|------------------|

|-----------|--------------------|----------------|------------------|

| wr_tid_p[1/0]                           | 2 | I | Y |        | Determines which thread is made available to the<br>write port. Unlike reads separate write ports can<br>access different threads. Indeed the two write ports<br>must have a different tid.                                                                                                                                                                                         |

|-----------------------------------------|---|---|---|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Save_(even)_addr<br>(odd/global)        | 2 | I | Y |        | Determines which shadow register (one of four)<br>receives the active register contents for the<br>(even/odd/global) bits. Only a single thread is<br>saved in any cycle. All active even registers for a<br>given tid are saved at the same time. Saves are a two<br>cycle operation. The save does not actually start<br>until one cycle after the address is flopped.            |

| save_local_addr                         | 3 | Ι | Y |        | Determines which shadow register (one of eight)<br>receives the active register contents for the local bits<br>(See save_even_addr for more detail).                                                                                                                                                                                                                                |

| save_(even)_en<br>(local/odd/global)    | 1 | Ι | Y |        | Enables saves for (even/local/odd/global) registers.<br>All enables can be asserted in same cycle.                                                                                                                                                                                                                                                                                  |

| save_tid                                | 2 | Ι | Y |        | Determines which thread will be saved for even/odd/local registers.                                                                                                                                                                                                                                                                                                                 |

| save_global_tid                         | 2 | Ι | Y |        | Determines which thread will be saved for global registers.                                                                                                                                                                                                                                                                                                                         |

| restore_(even)_addr<br>(odd/global)     | 2 | I | Y |        | Determines which shadow register (one of four)<br>updates the active register contents for the<br>(even/odd/global) bits. Only a single thread is<br>restored in any cycle. All active even registers for a<br>given tid are restored at the same time. Restores are<br>a two cycle operation. The restore does not actually<br>start until one cycle after the address is flopped. |

| restore_local_addr                      | 3 | Ι | Y |        | Determines which shadow register (one of eight)<br>updates the active register contents for the local bits<br>(See restore_even_addr for more detail).                                                                                                                                                                                                                              |

| restore_(even)_en<br>(local/odd/global) | 1 | Ι | Y |        | Enables restores for (even/local/odd/global)<br>registers. All enables can be asserted in same cycle.                                                                                                                                                                                                                                                                               |

| restore_tid                             | 2 | Ι | Y |        | Determines which thread will be restored for even/odd/local registers.                                                                                                                                                                                                                                                                                                              |

| restore_global_tid                      | 2 | Ι | Y |        | Determines which thread will be restored for global registers.                                                                                                                                                                                                                                                                                                                      |

| l2clk                                   | 1 | Ι | Ν | IO clk | Core clock                                                                                                                                                                                                                                                                                                                                                                          |

| tcu_aclk                                | 1 | Ι | Ν | tcu    | Scan In clock                                                                                                                                                                                                                                                                                                                                                                       |

| tcu_bclk                                | 1 | Ι | N | tcu    | Scan Out clock                                                                                                                                                                                                                                                                                                                                                                      |

| tcu_se_scancollar_in                    | 1 | Ι | N | tcu    | Scan enable for input flops. Controls shutting off input masters during macrotest.                                                                                                                                                                                                                                                                                                  |

| tcu_se               | 1 | Ι | N | tcu | Scan enable for array with exception of input flops.<br>This is the same as the scan enable to RTL flops.<br>This allows array to run for both macrotest and<br>LBIST but will shut off the L1clk during scanning.                                                                                                        |

|----------------------|---|---|---|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| clk_en               | 1 | Ι | Ν |     | pce to clock header used for local clock control to<br>shut off clock for functional or power saving<br>purposes                                                                                                                                                                                                          |

| tcu_pce_ov           | 1 | Ι | Ν | tcu | pce_ov to clock header used in override for scan of clk_en (pce) having turned clock off.                                                                                                                                                                                                                                 |

| tcu_clk_stop         | 1 | Ι | Ν | tcu | stop to clock header. This is an at speed signal                                                                                                                                                                                                                                                                          |

| tcu_array_wr_inhibit | 1 | Ι | N | tcu | Prevents array from writing, reading, or swaping.<br>Effectively "anded" with wr_en, rd_en, save_en, and<br>rsto_en. Turns off wordline and holds precharge for<br>swaps. Turns off wordline, column selects, and<br>holds precharge for writes. Turns off wordline and<br>holds precharge (not column select) for reads. |

| scan_in              | 1 | Ι | N |     | Block scan input. Latched on falling tcu_aclk edge.                                                                                                                                                                                                                                                                       |

| scan_out             | 1 | Ι | Ν |     | Block scan output. Launched on falling tcu_bclk edge.                                                                                                                                                                                                                                                                     |

TABLE 4-1

IRF Functional and DFT I/O Signal List (Continued)

# 4.4 Functional Operation

#### TABLE 4-2 IRF Modes of Operation

|      | Enable | Values |         | Memory Operation                                    | Output Results<br>(dout_p[2/1/0]) |

|------|--------|--------|---------|-----------------------------------------------------|-----------------------------------|

| read | write  | save   | restore |                                                     |                                   |

|      |        |        |         |                                                     |                                   |

| L    | L      | L      | L       | No Operation                                        | L                                 |

| Η    | L      | L      | L       | Read Cycle                                          | Results of Read                   |

| L    | Н      | L      | L       | Write Cycle                                         | L                                 |

| Н    | Н      | L      | L       | Read/Write Cycle with DOUT = X for the same address | Results of Read                   |

| L    | L      | Н      | L       | Save Cycle                                          | L                                 |

| Н    | L      | Н      | L       | Illegal                                             |                                   |